# 修士論文

# KamLAND2 に向けた 新型フロントエンド電子回路のトリガー開発

東北大学大学院理学研究科 物理学専攻

松本 優也

2024年

ニュートリノは素粒子の一種であり、現代のニュートリノ物理学においてニュートリノがマヨラナ粒子であるかどうかが大きな研究課題となっている。この検証方法にはニュートリノを伴わない二重  $\beta$  崩壊 ( $0\nu\beta\beta$  崩壊) の検出が考えられており、 $^{136}$ Xe を用いて行われている探索実験が KamLAND-Zen 実験である。KamLAND-Zen 実験では主な背景事象に Xe のニュートリノを伴う二重  $\beta$  崩壊による染み出しや宇宙線ミューオンによる Xe 核破砕で生成された不安定核の崩壊、Xe 容器における  $^{214}$ Bi の崩壊が挙げられる。これらの背景事象の減少を目指し、光電子量の増加によってエネルギー分解能を向上した KamLAND2 及び KamLAND2-Zen 実験が計画されている。宇宙線ミューオンによる不安定核の崩壊現象については核破砕による中性子を検出することによってタグする手法が用いられる。KamLAND2 ではトリガーシステムの刷新によって中性子検出効率を改善することによりタグ効率の向上が見込まれている。そのほか、将来的なソフトウェアによるイベント検出機能 (ソフトウェアトリガー) 実装による背景事象の減少が期待されている。

KamLAND2 へ向けて開発の進むトリガーシステムに導入される新型フロントエンド電子回路が MoGURA2 であり、その開発がこれまで進められてきた。MoGURA2 は FPGA による信号処理機能をもち、ここに搭載する論理回路 (ファームウェア) について開発が進められている。しかし、これまでの先行研究により開発されたファームウェアは MoGURA2 を 1 枚使用した単体系での動作テストを目的としたものであり、トリガーシステムのような共通する基準クロックによって複数枚の MoGURA2 が動作する系 (以下同期系) による運用には対応していない。そこで本研究では実際の KamLAND2 での運用を見越して MoGURA2 同期系による波形取得の実証を目的とした。

本研究ではトリガーインターフェースを新たに開発し、2 枚の MoGURA2 を用いたトリガーシステムによる同期性の検証を行なった。結果同期系による波形取得を確認するとともに、こうして取得されたデータの検出時刻についてレイテンシ差は目標値を達成しなかったもののジッターについては目標値を達成することを確認した。レイテンシ差については MoGURA2 を一枚用いた単体系においてタイルと呼ばれる ADC の構成単位に新たに同期機能を使うことで目標値を達成した。また、デジタイズレイテンシに対してオフセットを加える機能の検証および試験を行い、PMT のケーブル遅延の補正に利用可能であることを確認した。

# 目次

| 第1章 | 序論                             | 1  |

|-----|--------------------------------|----|

| 第2章 | ニュートリノ物理学                      | 3  |

| 2.1 | 素粒子標準模型                        | 3  |

| 2.2 | ニュートリノの発見                      | 4  |

|     | 2.2.1 ベータ崩壊                    | 4  |

|     | 2.2.2 ニュートリノの発見                | 4  |

|     | 2.2.3 ニュートリノのヘリシティ             | 4  |

| 2.3 | ニュートリノ振動とニュートリノの質量階層構造         | 5  |

|     | 2.3.1 太陽ニュートリノ問題               | 5  |

|     | 2.3.2 大気ニュートリノ異常               | 5  |

|     | 2.3.3 ニュートリノ振動の原理              | 5  |

|     | 2.3.4 原子炉ニュートリノ振動の観測           | 7  |

|     | 2.3.5 ニュートリノの質量階層構造            | 8  |

| 2.4 | ニュートリノとマヨラナ粒子                  | 9  |

|     | 2.4.1 ディラック質量とマヨラナ質量           | 9  |

|     | 2.4.2 シーソー機構                   | 11 |

| 2.5 | ニュートリノを伴わない二重ベータ崩壊によるマヨラナ性の検証  | 11 |

| 第3章 | KamLAND                        | 13 |

| 3.1 | 液体シンチレーター検出器 KamLAND           | 13 |

|     | 3.1.1 KamLAND の概要              | 13 |

|     | 3.1.2 KamLAND の構造              | 14 |

|     | 3.1.3 ニュートリノの検出原理              | 16 |

| 3.2 | KamLAND-Zen 実験                 | 17 |

|     | 3.2.1 KamLAND-Zen 実験における検出器の構造 | 18 |

|     | 3.2.2 KamLAND-Zen 400          | 19 |

|     | 3.2.3 KamLAND-Zen 800          | 19 |

|     | 3.2.4 KamLAND-Zen 実験における主な背景事象 | 19 |

<u>iv</u> 目次

|     | 3.2.5 | KamLAND2                          |

|-----|-------|-----------------------------------|

| 第4章 | KamL  | AND のデータ収集システムにおけるトリガーシステム 23     |

| 4.1 | KamD  | DAQ 24                            |

|     | 4.1.1 | KamFEE                            |

|     | 4.1.2 | トリガー                              |

|     | 4.1.3 | DAQ コンピューター                       |

| 4.2 | KamD  | OAQ のデッドタイムとミューオン信号               |

|     | 4.2.1 | オーバーシュート                          |

|     | 4.2.2 | アフターパルス 27                        |

|     | 4.2.3 | ミューオン核破砕反応による長寿命原子核               |

| 4.3 | MoGI  | DAQ 27                            |

|     | 4.3.1 | BLR                               |

|     | 4.3.2 | MoGURA                            |

|     | 4.3.3 | MoGURA trigger                    |

|     | 4.3.4 | 現行 MoGDAQ の課題点                    |

| 第5章 | KamL  | AND2 におけるトリガーシステムの概要 33           |

| 5.1 | トリガ   | 「ーシステムへの要求 33                     |

| 5.2 | KamL  | AND2 のトリガーシステムデザイン                |

|     | 5.2.1 | KamLAND2 へのトリガー導入計画               |

| 5.3 | KamL  | AND2 稼動初期を想定したトリガーシステムの構成 37      |

|     | 5.3.1 | 想定するトリガー導入段階                      |

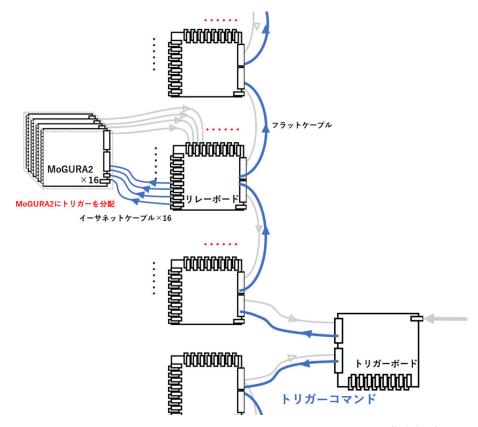

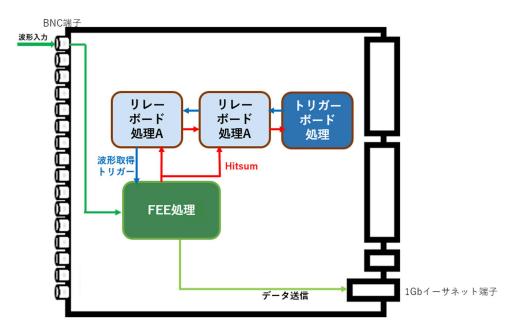

|     | 5.3.2 | トリガーシステム全体図                       |

|     | 5.3.3 | 想定される PMT 信号の特性                   |

|     | 5.3.4 | トリガーシステムの具体的な性能目標 40              |

|     | 5.3.5 | トリガーシステム動作概要 41                   |

|     | 5.3.6 | 主なトリガーフラグとトリガーコマンド 43             |

|     | 5.3.7 | 運用初期を想定したトリガーシステムのその他構想案 45       |

| 第6章 | トリガ   | iーシステムにおけるエレクトロニクスの開発現状と本研究の目的 47 |

| 6.1 | トリガ   | 「ーシステムに向けて新たに開発されるエレクトロニクス 47     |

| 6.2 | 新型フ   | プロントエンド電子回路 MoGURA2 47            |

|     | 6.2.1 | MoGURA2 の性能と先行研究         48       |

|     | 6.2.2 | MoGURA2         に実装されている主な入出力端子   |

|     | 6.2.3 | クロック信号供給部 52                      |

|     | 6.2.4 | アナログ子基板 53                        |

|     | 6.2.5 | LADC                              |

|     | 6.2.6 | RFSoC と FPGA ファームウェア              |

| バック        | エンドに用いるエレクトロニクス                                                                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

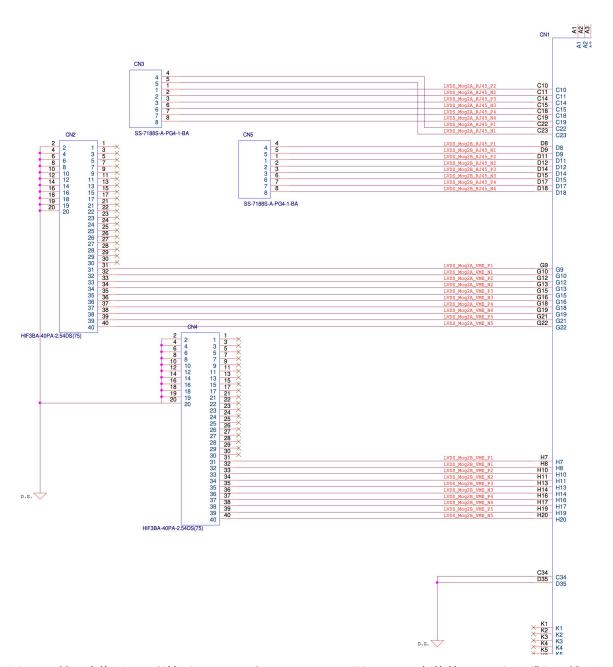

| 6.3.1      | リレーボードのデザイン                                                                                                                                                                                     |

| 6.3.2      | トリガーボードのデザイン                                                                                                                                                                                    |

| MoGU       | IRA2 を用いたトリガーシステムの現状                                                                                                                                                                            |

| 6.4.1      | <b>MoGURA2</b> 単体系での動作試験                                                                                                                                                                        |

| 本研究        | の目的                                                                                                                                                                                             |

| 6.5.1      | 同期系における目標性能                                                                                                                                                                                     |

| 6.5.2      | 本研究の流れ                                                                                                                                                                                          |

| MoGU       | RA2 同期系による同期波形取得のための FPGA ロジック開発                                                                                                                                                                |

| トリガ        | ーシステム実現のために必要な要素                                                                                                                                                                                |

| 7.1.1      | すでに開発されている機能                                                                                                                                                                                    |

| 7.1.2      | 新たに実装する機能・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                   |

| 本研究        | にて実装した FPGA ロジック                                                                                                                                                                                |

| 7.2.1      | MoGURA2 への搭載を想定した波形バッファリングモジュール                                                                                                                                                                 |

| 7.2.2      | トリガーボードロジック                                                                                                                                                                                     |

| 7.2.3      | リレーボードロジック                                                                                                                                                                                      |

| 本研究        | にて作成した <b>FPGA</b> ロジックの位置付け                                                                                                                                                                    |

| MoGU       | RA2 単体系における動作試験                                                                                                                                                                                 |

| トリガ        | ーロジックの動作確認試験方法                                                                                                                                                                                  |

| 8.1.1      | MoGURA2 に搭載した FPGA ファームウェア                                                                                                                                                                      |

| 8.1.2      | 本試験における実験系                                                                                                                                                                                      |

| MoGU       | <br> RA2 単体系のトリガー試験結果                                                                                                                                                                           |

| 8.2.1      | 本研究にて作成したトリガーコマンド用インターフェースを用いた波形                                                                                                                                                                |

|            | 取得結果....................................                                                                                                                                                        |

| 8.2.2      | バッファリングモジュールの動作確認                                                                                                                                                                               |

| MoGU       | RA2 同期系における波形取得試験                                                                                                                                                                               |

| 同期試        | 験の目的                                                                                                                                                                                            |

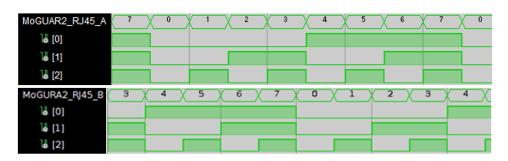

| 本研究        | において使用するエレクトロニクス                                                                                                                                                                                |

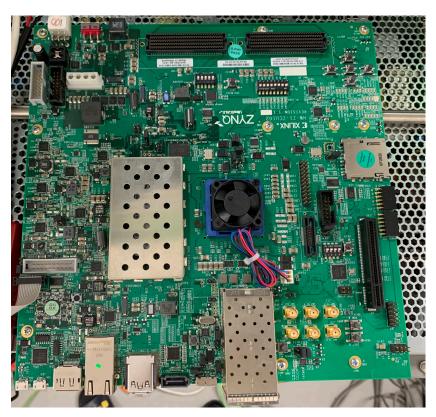

| 9.2.1      | <b>ZCU102</b> 評価ボード                                                                                                                                                                             |

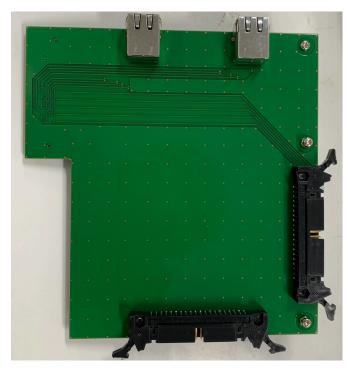

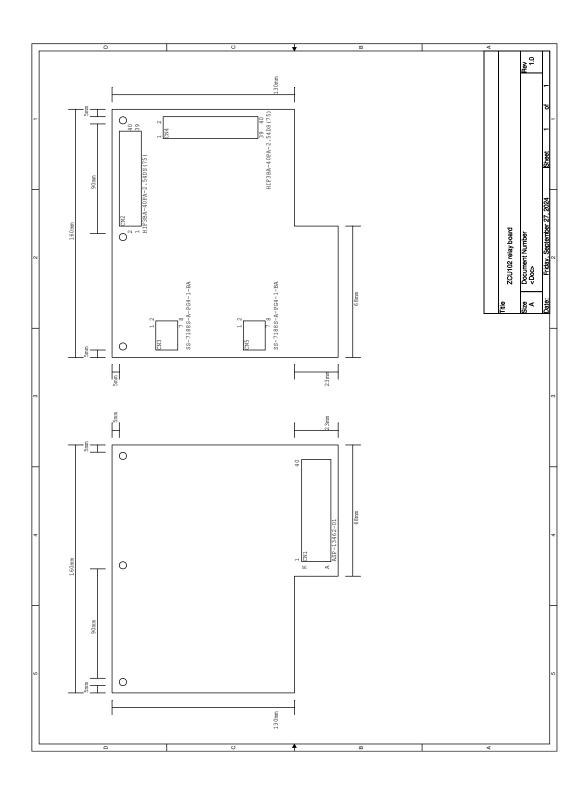

| 9.2.2      | <b>ZCU102</b> 端子変換用ボード                                                                                                                                                                          |

| 9.2.3      | 外部クロック駆動の MoGURA2                                                                                                                                                                               |

| MoGU       | RA2 の同期試験における波形取得系                                                                                                                                                                              |

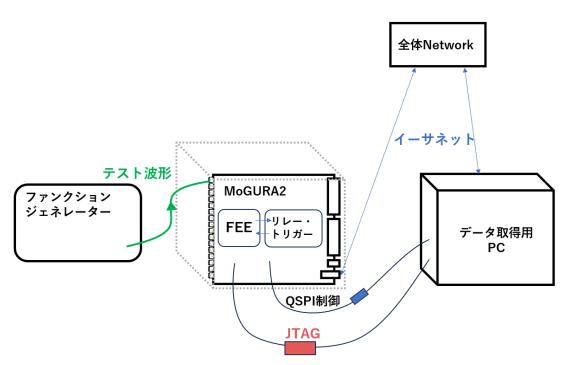

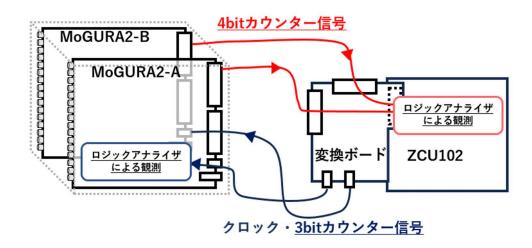

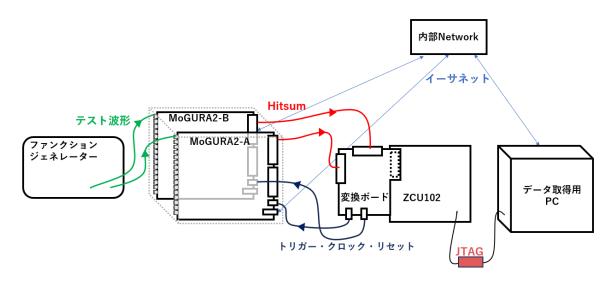

| 9.3.1      | 同期試験における波形取得系の概要図                                                                                                                                                                               |

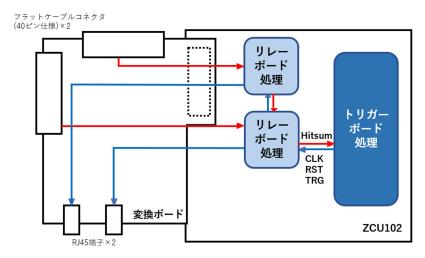

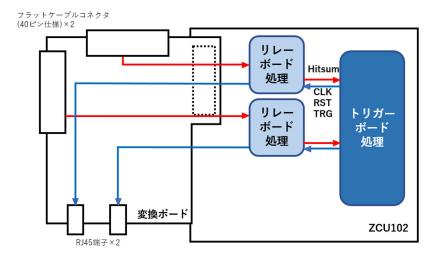

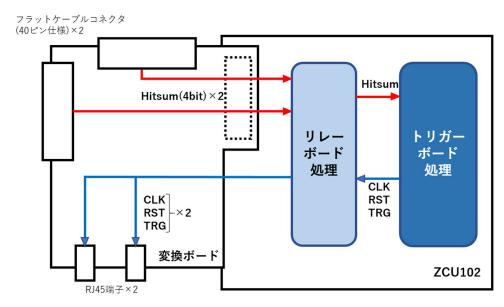

| 9.3.2      | <b>ZCU102</b> によるトリガーボードの代用                                                                                                                                                                     |

| · ·· · · - |                                                                                                                                                                                                 |

| 9.3.3      | 外部 PC による操作                                                                                                                                                                                     |

|            | 6.3.1<br>6.3.2<br>MoGU<br>6.4.1<br>6.5.1<br>6.5.2<br>MoGU<br>7.1.1<br>7.2.3<br>本 MoGU<br>7.2.3<br>本 MoGU<br>8.1.1<br>8.2.2<br>MoGU<br>8.2.1<br>8.2.2<br>MoGU<br>9.2.1<br>9.2.3<br>MoGU<br>9.3.1 |

<u>vi</u> 目次

|        | 9.3.5 | 同期系の起動方法                       | 82 |

|--------|-------|--------------------------------|----|

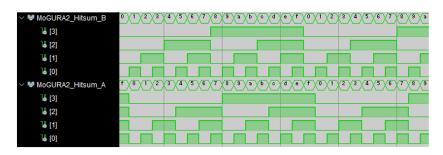

| 9.4    | 波形取   | 得結果と同期精度                       | 83 |

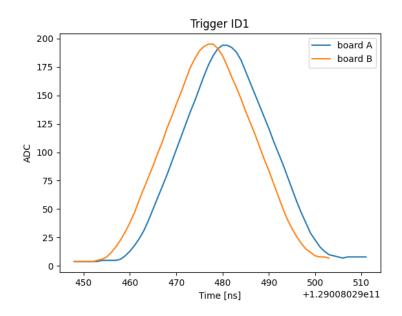

|        | 9.4.1 | 波形観測結果                         | 83 |

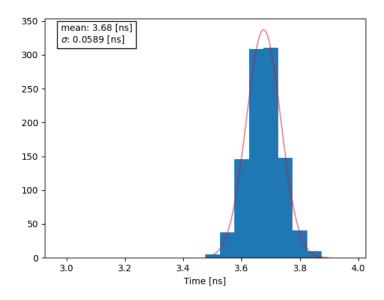

|        | 9.4.2 | 時間分布及びデジタイズの同期評価               | 83 |

| 9.5    | RFDC  | ドライバーによるタイル間のデジタイズ同期           | 85 |

|        | 9.5.1 | Multi Tile Sync 機能             | 85 |

|        | 9.5.2 | RFADC の動作不良                    | 85 |

|        | 9.5.3 | 単ボード系における Multi Tile Sync 動作試験 | 85 |

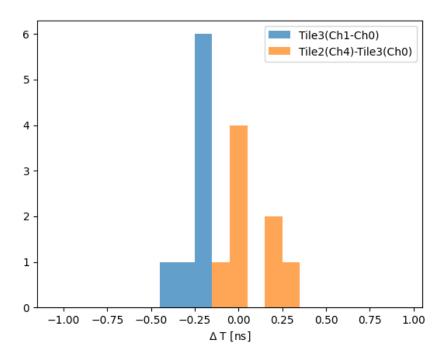

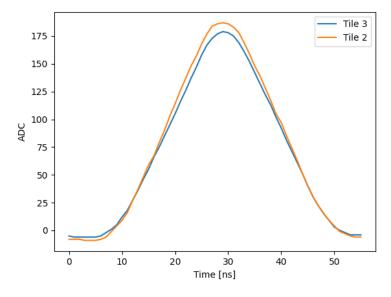

|        | 9.5.4 | Multi Tile Sync 動作試験結果         | 86 |

| 9.6    | レイテ   | ンシのオフセット設定                     | 88 |

|        | 9.6.1 | 単ボード系におけるレイテンシのオフセット制御試験       | 88 |

|        | 9.6.2 | レイテンシのオフセット制御試験結果              | 88 |

|        | 9.6.3 | オフセット制御による PMT のケーブル遅延補正       | 89 |

| 第 10 章 | 結論と   | ー<br>今後の課題                     | 91 |

| 10.1   | 結論    |                                | 91 |

| 10.2   |       | 課題                             | 92 |

| 付録     |       |                                | 95 |

| A      | 端子変   | 換ボードの設計概要                      | 95 |

| 謝辞     |       |                                | 99 |

# 図目次

| 2.1  | <b>KamLAND</b> 実験にて観測されたニュートリノ振動                | 8  |

|------|-------------------------------------------------|----|

| 2.2  | 二重ベータ崩壊の概略図・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 12 |

|      |                                                 |    |

| 3.1  | 池の山地下に建設された <b>KamLAND</b>                      | 13 |

| 3.2  | KamLAND の内部構造                                   | 14 |

| 3.3  | PMT の内部構造                                       | 15 |

| 3.4  | KamLAND で使用されている PMT の外形図                       | 16 |

| 3.5  | 逆ベータ崩壊反応                                        | 17 |

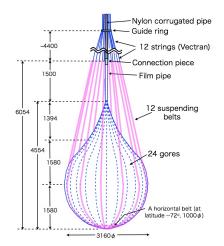

| 3.6  | KamLAND-Zen 実験で使用された検出器のセットアップ                  | 18 |

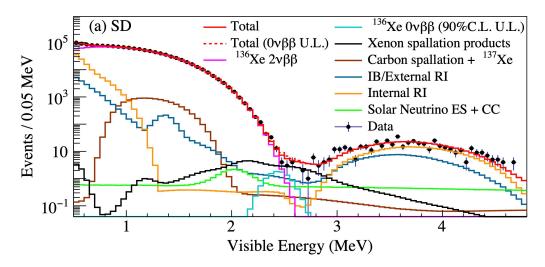

| 3.7  | KamLAND-Zen800 によって得られたエネルギースペクトル               | 19 |

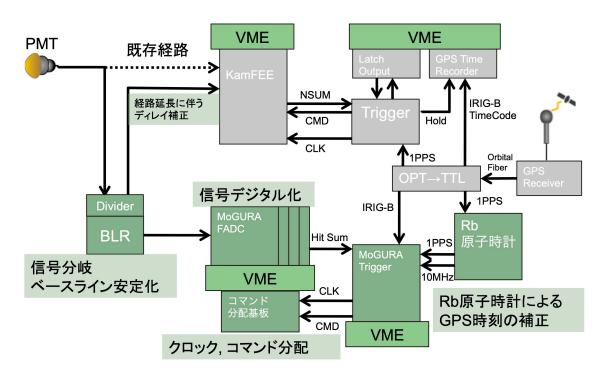

| 4.1  | KamLAND のデータ DAQ 全体像                            | 23 |

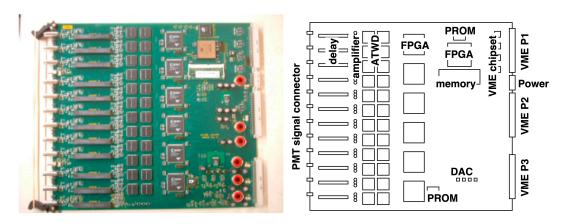

| 4.2  | KamFEE のボード外見写真実装部品の配置図                         | 24 |

| 4.3  | <b>KamFEE</b> のブロックダイアグラム                       | 25 |

| 4.4  | ミューオン信号と直後に見られるオーバーシュート及びアフターパルス                | 26 |

| 4.5  | PMT のブリーダ回路                                     | 26 |

| 4.6  | ミューオン信号に対する BLR 処理の概略図                          | 28 |

| 4.7  | <b>MoGURA</b> ボードと主な実装部品                        | 28 |

| 4.8  | ミューオン信号後の NHit 分布                               | 30 |

| 4.9  | <b>ΔNHit</b> の算出                                | 31 |

| 4.10 | MoGDAQ にて観測されたミューオン後の中性子捕獲事象と不安定核種の寿命に          |    |

|      | よりフィットした中性子捕獲事象数                                | 32 |

| 5.1  | ハードウェアトリガーの概念図                                  | 36 |

| 5.2  | マルチレベルトリガーの概念図                                  | 36 |

| 5.3  | ソフトウェアトリガーの概念図                                  | 37 |

| 5.4  | トリガーシステム模式図                                     | 38 |

| 5.5  | 典型的な 1p.e. 波形                                   | 39 |

| 5.6  | トリガーシステムにおけるクロック信号及び TC リセットの分配経路               | 42 |

| 5.7  | トリガーシステムにおける Hitsum の分配経路                       | 43 |

**viii** 図目次

| 5.8  | トリガーシステムにおけるトリガーの分配経路 44                          |

|------|---------------------------------------------------|

| 6.1  | MoGURA2       に搭載されている主な部品                        |

| 6.2  | <b>MoGURA2</b> へのクロック入力に用いる <b>RJ45</b> コネクタのピン配置 |

| 6.3  | MoGURA2 のクロック系統図 53                               |

| 6.4  | アナログ子基板写真 54                                      |

| 6.5  | アナログ子基板による信号の分岐及び増幅の概念図                           |

| 6.6  | MoGURA2 のデータフレームフォーマット                            |

| 6.7  | 現在想定されているリレーボードのデザイン57                            |

| 6.8  | 現在想定されているトリガーボードのデザイン 57                          |

| 6.9  | 現在波形取得が可能となっている系 58                               |

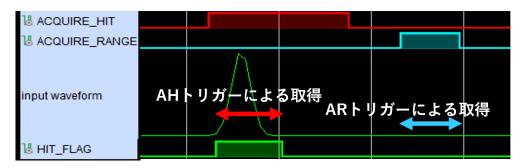

| 7.1  | トリガーコマンドによる波形取得範囲63                               |

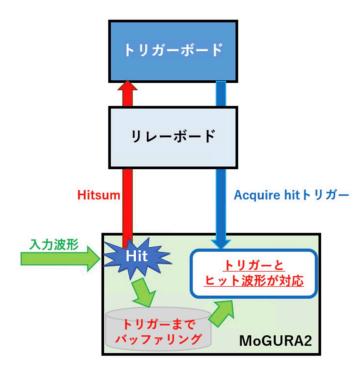

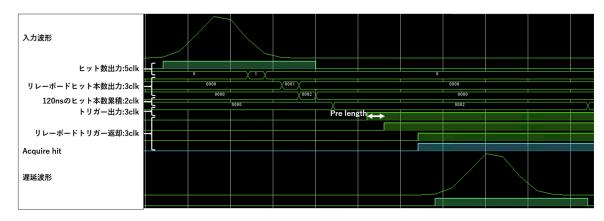

| 7.2  | トリガーシステムにおける波形バッファリング64                           |

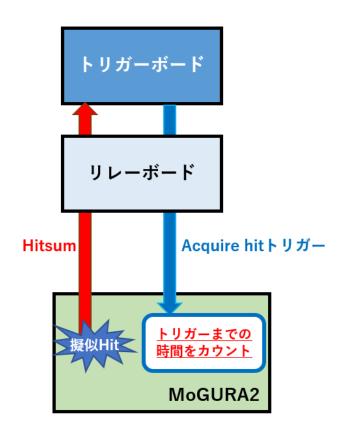

| 7.3  | バッファリング時間のキャリブレーション模式図 66                         |

| 8.1  | トリガー試験で用いたファームウェアの概念図 70                          |

| 8.2  | トリガー試験で用いた実験系                                     |

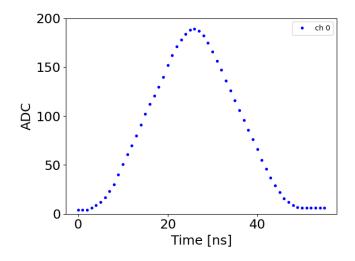

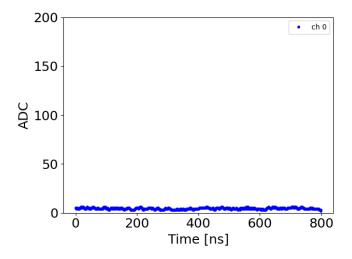

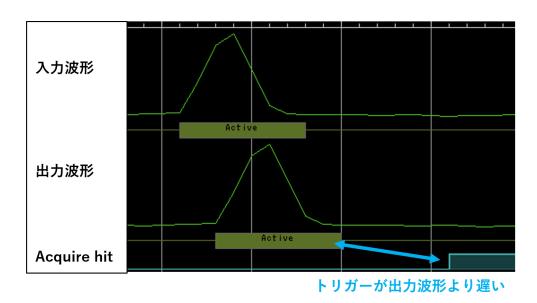

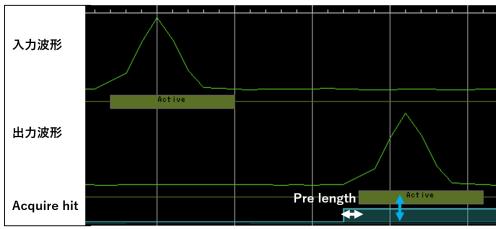

| 8.3  | Acquire hit トリガーの動作確認結果                           |

| 8.4  | Acquire range トリガーの動作確認結果                         |

| 8.5  | キャリブレーション前のバッファリングモジュールの動作 72                     |

| 8.6  | キャリブレーション後のバッファリングモジュールの動作 73                     |

| 8.7  | シミュレーションによるバッファリングモジュールの動作 73                     |

| 9.1  | <b>ZCU</b> 102 評価ボードの外見図                          |

| 9.2  | <b>ZCU</b> 102 端子変換用ボード                           |

| 9.3  | 端子変換用ボードの動作確認の様子 78                               |

| 9.4  | フラットケーブル用コネクタ動作結果                                 |

| 9.5  | 端子変換用ボード搭載の RJ45 コネクタ動作結果                         |

| 9.6  | 同期試験に使用した MoGURA2 用ファームウェア 79                     |

| 9.7  | MoGURA2 同期試験における実験系                               |

| 9.8  | <b>ZCU102</b> による試験が可能な接続系の例                      |

| 9.9  | 同期試験に用いる <b>ZCU</b> 102 のファームウェア概念図 82            |

| 9.10 | MoGURA2 同期系において 2 枚のボードで観測された波形 84                |

| 9.11 | MoGURA2 同期系において各ボードでデジタイズされた波形の時間差分布のヒ            |

|      | ストグラム                                             |

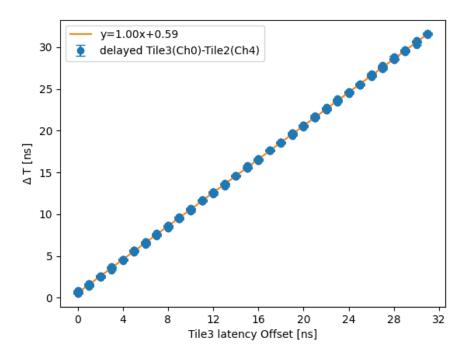

| 9.12 | タイル間同期機能によるデジタイズのレイテンシ差分布87                       |

| 9.13 | タイル間同期後の取得波形の一例                                   |

| 9.14 | デジタイズレイテンシに対するオフセット制御機能の検証結果 89                   |

|     |                                                | <u>ix</u> |

|-----|------------------------------------------------|-----------|

| A.1 | 端子変換ボード外形図.................................... | 96        |

| A.2 | 端子変換ボード配線図.................................... | 97        |

# 表目次

| 2.1 | 素粒子標準模型におけるフェルミ粒子              | 3  |

|-----|--------------------------------|----|

| 2.2 | 素粒子標準模型におけるボーズ粒子               | 4  |

| 2.3 | 測定されているニュートリノ振動パラメータ           | 9  |

| 3.1 | Kam-LS の成分表                    | 16 |

| 3.2 | バッファーオイルの成分表                   | 16 |

| 3.3 | Xe-LS の成分表                     | 18 |

| 4.1 | <b>MoGURA</b> の各ゲインチャンネル       | 29 |

| 5.1 | 旧トリガーシステムとトリガーシステムのオンボードメモリ容量  | 34 |

| 6.1 | <b>MoGURA2</b> の各ゲインによるデジタイズ性能 | 49 |

| 6.2 | MoGURA2 に搭載されているオンボードメモリ       | 56 |

| 9.1 | 同期試験において設定したパラメータ              | 80 |

| 9.2 | トリガースイッチ機能の概要                  | 82 |

# 第1章

# 序論

物質を構成する最小構成単位である素粒子を研究する学問として、素粒子物理学がこれまで発展してきた。現代の素粒子物理学は素粒子標準模型を基礎としており、物質を構成する素粒子は計 12 種類のクォークとレプトンであることがわかっている。ニュートリノは標準模型において3世代存在するレプトンであり、標準模型においてはその質量を持たない。しかしニュートリノはそのフレーバーが変化するニュートリノ振動現象の観測により、非常に小さいが有限の質量を持つことが明らかとなった。ニュートリノの非常に小さい質量は素粒子標準模型によって説明することができず、新しい物理の枠組みを必要とすることを意味している。

ニュートリノの非常に小さい質量を自然に説明する方法として、ニュートリノがマヨラナ粒子であると仮定するものがある。マヨラナ粒子は他の素粒子が属するディラック粒子と異なる過程によってマヨラナ質量を獲得する。また粒子と反粒子が同一であるという性質を持ち、シーソー機構によってその質量を非常に小さくすることが可能である。

ニュートリノがマヨラナ粒子であることの検証には、ニュートリノを伴わない二重ベータ崩壊  $(0\nu\beta\beta$  崩壊) の検出が考えられている。 $0\nu\beta\beta$  崩壊は二重ベータ崩壊時に生じた 2 つのニュートリノがマヨラナ粒子であることによって対消滅することで実現し、この現象が観測されればニュートリノがマヨラナ粒子であるということの証明となる。現在までさまざまな実験によって  $0\nu\beta\beta$  崩壊の探索が行われているが発見されていない。

KamLAND-Zen 実験とは、液体シンチレーター検出器 Kamioka Liquid-scintilator-Anti-Neutrino Detector (KamLAND) によって行われていた  $0\nu\beta\beta$  崩壊の探索実験である。二重ベータ崩壊核として  $^{136}$ Xe を使用しており、その使用量によって KamLAND-Zen 400 (Zen 400) と KamLAND-Zen 800 (Zen 800) という二つの実験期間に分けられる。Zen 400 と Zen 800 の結果を合わせることで、 $0\nu\beta\beta$  崩壊の半減期について  $T_{0\nu\beta\beta}^{1/2}>3.8\times10^{26}$  year という制限を与えた [1]。主な背景事象には  $2\nu\beta\beta$  崩壊の染み出しや宇宙線ミューオンによる Xe 核破砕によって生成された不安定核の崩壊、Xe 容器における  $^{214}$ Bi の崩壊があり、これらの背景事象減少が課題となった。

KamLAND-Zen 実験は 2024 年に終了し、現在は KamLADN2-Zen 実験が計画されている。 実験を行う KamLAND2 検出器は KamLAND-Zen 実験の背景事象をふまえ、光電子量の増加 によるエネルギー分解能の向上や中性子検出効率の改善による不安定核検出効率の向上、シンチ 第 1 章 序論

レーションバルーン導入による Xe 容器付近のイベント検出を目指したアップデートが加えられる。トリガーシステムについてはその刷新によって KamLAND のトリガーシステムにおける課題点を克服し、宇宙線ミューオンによる Xe 核破砕で生じる不安定核の崩壊のタグ率向上が期待されている。このトリガーシステムについては、フロントエンドおよびバックエンドの両面から開発が進められている。

現在、トリガーシステムのエレクトロニクスのうち新型フロントエンド電子回路 (MoGURA2) の基板設計および製造がされている。MoGURA2 は Field Programmable Gate Array (FPGA) を搭載しており、コーディングによって実装した論理回路によって信号処理を行う。こうして実装された論理回路はファームウェアと呼ばれており、開発が進められている。これまで開発されたファームウェアは MoGURA2 を 1 枚使用した系 (以下単体系) における動作テストを目的としたものであり、より実際のトリガーシステムに近い複数のボードが共通の基準クロック信号によって駆動する系 (以下同期系) による動作テストは実施されていない。そこで、本研究では KamLAND2 での運用に向けて MoGURA2 の同期系による同期した波形取得の実証を目的とする。そのために、2 枚の MoGURA2 ボードとトリガー回路を模擬した Xilinx 評価ボード(ZCU102)1 枚を組み合わせたシステムを作り、同期波形取得の実証試験を行い同期性の検証を行った。トリガーシステムの同期目標値については KamLAND2 の検出器系を考慮し、同時信号の検出に対して、ジッターは 0.1 ns、レイテンシ差は 1 ns とした。その後、MoGURA2 単体系に対し新たにタイル間同期機能を使い、ADC の構成単位であるタイル間でのデジタイズ同期やデジタイズレイテンシの制御を試みた。

# 第2章

# ニュートリノ物理学

ここでは、KamLAND 及び KamLAND2 にて観測対象としているニュートリノの物理的背景について述べる。

# 2.1 素粒子標準模型

物質の根源を明らかにする素粒子分野において、標準模型と呼ばれる理論が確立し現在の物理学の基礎となっている。標準模型において素粒子は 17 種類存在し、粒子のスピンが半整数であるフェルミ粒子と整数であるボーズ粒子に分けられる。表 2.1 に示すようにフェルミ粒子については現在 12 種類発見されており、強い相互作用をするクォークと強い相互作用をしないレプトンに分けられている。ボーズ粒子については表 2.2 に示す 5 種類が発見されている。

標準模型においてニュートリノはフェルミ粒子のレプトンに属しており、唯一電荷を持たないことや他の素粒子と比べて質量を持たないといった特徴から検出が難しい粒子であった。なお、ニュートリノの質量については 2.3 章のニュートリノ振動以降で詳しく説明する。

|      | スピン                      | 電荷             | 第一世代        | 第二世代       | 第三世代       |

|------|--------------------------|----------------|-------------|------------|------------|

| クォーク | 1                        | $+\frac{2}{3}$ | u           | c          | t          |

| クォーク | $\frac{\overline{2}}{2}$ | $-\frac{1}{3}$ | d           | S          | b          |

| レプトン | 1                        | -1             | e           | $\mu$      | au         |

|      | $\frac{1}{2}$            | 0              | $ u_{ m e}$ | $ u_{\mu}$ | $ u_{	au}$ |

表 2.1: 素粒子標準模型におけるフェルミ粒子

|        | スピン | 電荷 | 粒子       | 備考           |  |

|--------|-----|----|----------|--------------|--|

| ゲージ粒子  | 1   | 0  | g        | 強い相互作用を媒介    |  |

|        |     | 0  | $\gamma$ | 電磁相互作用を媒介    |  |

|        |     | 0  | Z        | 弱い相互作用を媒介    |  |

|        |     | ±1 | W        |              |  |

| スカラー粒子 | 0   | 0  | Н        | 粒子の質量獲得機構に関与 |  |

表 2.2: 素粒子標準模型におけるボーズ粒子

# 2.2 ニュートリノの発見

## 2.2.1 ベータ崩壊

ニュートリノの導入の起源は 1930 年代に遡る。当時は原子核のベータ崩壊について、原子と電子の二体反応であると考えられており、放出される電子のエネルギー分布について特定のピークを持つことが予想されていた。しかし、測定により電子のエネルギーについて連続分布が得られており、このことは物理学における大きな謎であった。

そこで、パウリはベータ崩壊について式 2.1 のように観測できない粒子が関わる 3 体反応であるという仮説を立てた。ここで導入された粒子がニュートリノである。

$$M(Z, A) \to D(Z + 1, A) + e^{-} + \bar{\nu}_{e}$$

(2.1)

## 2.2.2 ニュートリノの発見

その後、パウリによって仮想的に導入された粒子であったニュートリノは Reines と Cowan の 実験によって観測された。実験手法は、液体シンチレーター検出器を用いた陽電子の対消滅及び 中性子の遅延同時計測であり、原子炉から放出されるニュートリノが以下の式 2.2 で表される逆 ベータ崩壊反応によって観測される。

$$\bar{\nu}_{\rm e} + {\rm p} \rightarrow {\rm e}^+ + {\rm n}$$

(2.2)

# 2.2.3 ニュートリノのヘリシティ

ニュートリノのヘリシティについては、Goldhaber らによって測定された。Goldharber らは、以下の式で表される  $^{152}$ Eu による電子捕獲反応を用いた。

$$^{152}\text{Eu} + \text{e}^- \to \nu_{\text{e}} + ^{152}\text{Sm}^* \to ^{152}\text{Sm} + \gamma$$

(2.3)

始状態について、 $^{152}$ Eu のスピン角運動量は 0、K 殻の捕獲電子は l=0 である。中間状態の $^{152}$ Sm $^*$  のスピンパリティが  $1^-$  であることを考慮すると、ニュートリノ及び光子の角運動量は

$(J_{\nu}, J_{\gamma}) = (+1/2, -1)or(-1/2, +1)$  のいずれかに制限される。その後、光子の偏光状態についての測定からニュートリノのヘリシティが決定され、全てのニュートリノについて左巻き (J = -1) であるという結果が得られた。また、反ニュートリノについては右巻きのみが観測されている。

# 2.3 ニュートリノ振動とニュートリノの質量階層構造

# 2.3.1 太陽ニュートリノ問題

ニュートリノが次に用いられたのは、標準太陽模型の検証であった。太陽内部では核融合によって太陽ニュートリノが生じており、次式のように表すことができる。

$$2e^{-} + 4p \rightarrow^{4} He + 2\nu_{e} + \gamma$$

(2.4)

Davis は、テトラクロロエチレンによるニュートリノ捕獲反応を用いることで、この太陽ニュートリノの検出を試みた。反応式は以下のように表され、生じた <sup>37</sup>Ar の逆反応によって放出されるオージェ電子を検出することでニュートリノの直接検出に成功した。

$$\nu_{\rm e} + ^{37} {\rm Cl} \rightarrow ^{37} {\rm Ar} + {\rm e}^- + 26.7 {\rm MeV} - {\rm E}_{\nu}$$

(2.5)

しかし、この実験によって得られた太陽ニュートリノフラックスは標準太陽模型による理論予測のわずか3分の1であった。この理論予測と実験による検出量の不一致は太陽ニュートリノ問題と呼ばれニュートリノ物理学における課題となった。

## 2.3.2 大気ニュートリノ異常

太陽ニュートリノ問題と並んで理論によって説明ができなかった問題が、大気ニュートリノ異常である。大気ニュートリノとは、空気中の原子が宇宙線によって破壊されることで生じるニュートリノである。宇宙線の衝突によってパイオンが生成され、以下の崩壊によってニュートリノが生成される。

$$\pi^{\pm} \to \mu^{\pm} + \nu_{\mu}/\bar{\nu}_{\mu} \tag{2.6}$$

$$\mu^{\pm} \to e^{\pm} + \bar{\nu}_{\mu}/\nu_{\mu} + \nu_{e}/\bar{\nu}_{e}$$

(2.7)

ここで  $\pi^\pm$  の生成量が等しいと仮定すると、この過程における  $\nu_e+\bar{\nu}_e$ 、 $\nu_\mu+\bar{\nu}_\mu$  の比はパイオン の生成量の絶対値によらず 1:2 となる。そこで、 $R=(\nu_e+\bar{\nu}_e)/(\nu_\mu+\bar{\nu}_\mu)$  という値を指標とし、理論による値と実験による観測結果との比較が行われた。この解析では、理論値に比べ観測結果 が小さいという結果が得られ、この理論予測と観測結果の不一致は大気ニュートリノ異常と呼ばれた。

## 2.3.3 ニュートリノ振動の原理

先に説明した太陽ニュートリノ問題及び大気ニュートリノ異常の説明のため、ニュートリノ振動という現象の仮説が立てられた。ただし、ニュートリノに対し質量を導入しなければならず、標準模型に反する仮定のもとに導出される現象である。

#### 一般的なニュートリノ振動

ニュートリノが質量を持たない場合、フレーバー固有状態がニュートリノの質量固有状態と一致する。ニュートリノに質量を導入すると、フレーバー固有状態と質量固有状態が一致せず、両者が混合する。以下では、3世代の場合を考える。

ニュートリノのフレーバー固有状態を  $|\nu_{\alpha}\rangle$  質量固有状態を  $|\nu_{i}\rangle$  と表すと、正規直交した各固有 状態においてフレーバー固有状態はユニタリ混合行列 U の要素を用いて

$$|\nu_{\alpha}\rangle = \sum_{i} U_{\alpha i} |\nu_{i}\rangle \tag{2.8}$$

と書ける。質量固有状態は

$$|\nu_i\rangle = \sum_{\alpha} (U^{\dagger})_{i\alpha} |\nu_{\alpha}\rangle = \sum_{\alpha} U_{\alpha i}^* |\nu_{\alpha}\rangle \tag{2.9}$$

と表される。混合行列  $U=U_{MNSP}$  はユニタリ行列であり、具体的な形式について以下のように表される。

$$U_{MNSP} = \begin{pmatrix} U_{e1} & U_{e2} & U_{e3} \\ U_{\mu 1} & U_{\mu 2} & U_{\mu 3} \\ U_{\tau 1} & U_{\tau 2} & U_{\tau 3} \end{pmatrix}$$

$$= \begin{pmatrix} 1 & 0 & 0 \\ 0 & c_{23} & s_{23} \\ 0 & -s_{23} & c_{23} \end{pmatrix} \begin{pmatrix} c_{13} & 0 & s_{13}e^{-i\delta_{\nu}} \\ 0 & 1 & 0 \\ s_{13}e^{i\delta_{nu}} & 0 & c_{13} \end{pmatrix} \begin{pmatrix} c_{12} & s_{12} & 0 \\ -s_{12} & c_{12} & 0 \\ 0 & 0 & 1 \end{pmatrix}$$

$$= \begin{pmatrix} c_{13}c_{12} & c_{13}s_{12} & s_{13}e^{-i\delta_{\nu}} \\ -s_{12}s_{13}c_{12}e^{i\delta_{\nu}} - c_{23}s_{12} & -s_{23}s_{13}s_{12}e^{i\delta_{\nu}} + c_{23}c_{12} & s_{23}c_{13} \\ -c_{23}s_{13}c_{12}e^{i\delta_{\nu}} + s_{23}c_{12} & -c_{23}s_{13}s_{12}e^{i\delta_{\nu}} + s_{23}c_{12} & c_{23}c_{13} \end{pmatrix}$$

$$(2.10)$$

ただし、 $s_{ij}=sin\theta_{ij},c_{ij}=cos\theta_{ij}$ であり、混合角  $\theta_{ij}$  及び CP 対称性の破れ  $\delta$  を用いた。ここで、質量固有状態はエネルギー固有状態となっており、シュレディンガー方程式を満たす定常状態となることより時間発展は

$$|\nu_i(x,t)\rangle = e^{-iE_it} |\nu_i(x,0)\rangle \tag{2.11}$$

と表される。式 2.8 及び式 2.9 を用いるとフレーバー固有状態の時間発展は

$$|\nu_{\alpha}(x,t)\rangle = \sum_{i} U_{\alpha i} e^{-iE_{i}t} |\nu_{i}(x,0)\rangle = \sum_{i,\beta} U_{\beta i} U_{\alpha i}^{*} e^{ipx} e^{-iE_{i}t} |\nu_{\beta}(x,0)\rangle$$

(2.12)

のように書ける。ただし、エネルギーについて質量が十分小さい場合の近似  $E_i=\sqrt{{m_i}^2+{p_i}^2}\simeq p_i+\frac{{m_i}^2}{2p_i}\simeq E+\frac{{m_i}^2}{2E}$  を用いた。フレーバー  $\alpha$  から  $\beta$  への遷移振幅は

$$A(\nu_{\alpha} \to \nu_{\beta})(t) = \langle \nu_{\beta} | \nu(x, t) \rangle = \sum_{i} U_{\beta i}^{*} U_{\alpha i} e^{ipx} e_{i} E_{i} t$$

$$\simeq \sum_{i} U_{\beta i}^{*} U_{\alpha i} \exp\left(-i \frac{m_{i}^{2}}{2} \frac{L}{E}\right) = A(\alpha \to \beta)(L)$$

(2.13)

のように表される。ただし、距離 x については長さ L だけ離れた検出器による観測の場合を考え、 x=L と置き換えを行なった。遷移確率 P は遷移振幅 A から

$$P(\nu\alpha \to \nu\beta)(t) = |A(\alpha \to \beta)|^2 = \sum_{i} \sum_{j} U_{\alpha i} U_{\alpha j}^* U_{\beta i}^* U_{\beta j} e^{-i(E_i - E_j)t}$$

$$= \sum_{i} |U_{\alpha i} U_{\beta i}^*|^2 + 2Re \sum_{j>i} U_{\alpha i} U_{\alpha j}^* U_{\beta i}^* U_{\beta j} \exp\left(-i\frac{\Delta m_{ij}^2}{2}\right) \frac{L}{E}$$

$$= \delta_{\alpha\beta} - 4 \sum_{j>i} U_{\alpha i} U_{\alpha j}^* U_{\beta i}^* U_{\beta j} \sin^2\left(\frac{\Delta m_{ij}^2}{4} \frac{L}{E}\right)$$

(2.14)

のように求められる。ただし、

$$\Delta m_{ij}^{2} = m_{i}^{2} - m_{j}^{2} \tag{2.15}$$

である。以上のように、ニュートリノが距離 L 進むときにそのフレーバーに遷移確率が現れることがわかる。

# 2.3.4 原子炉ニュートリノ振動の観測

原子炉では、核燃料の燃焼によって反電子ニュートリノが放出される。原子炉ニュートリノは原子炉の稼働情報を用いることでその生成量を予測する事ができるため、ニュートリノ振動の観測に適していると考えられた。この原子炉ニュートリノ振動を想定し、電子型のニュートリノにおけるニュートリノ振動について定式化を行う。式 2.14 より、電子ニュートリノが長さ L 進んだ先で電子型である確率  $\mathbf{P}$  は  $\alpha,\beta$  に  $\mathbf{e}$  を代入して

$$P(\nu_e \to \nu_e)(t) = \delta_{ee} - 4 \sum_{j>i} U_{ei} U_{ej}^* U_{ei}^* U_{ej} \sin^2 \left( \frac{\Delta m_{ij}^2}{4} \frac{L}{E} \right)$$

$$= 1 - 4c_{13}^4 c_{12}^2 s_{12}^2 \sin^2 \left( \frac{\Delta m_{12}^2}{4} \frac{L}{E} \right)$$

$$- 4c_{13}^2 c_{12}^2 s_{13}^2 \sin^2 \left( \frac{\Delta m_{13}^2}{4} \frac{L}{E} \right) - 4c_{13}^2 s_{12}^2 s_{13}^2 \sin^2 \left( \frac{\Delta m_{23}^2}{4} \frac{L}{E} \right)$$

(2.16)

と求められる。実験より $sin^2\theta_{13}$ は非常に小さいことが知られており、この時

$$P(\nu_e \to \nu_e)(t) \sim 1 - 4c_{13}^4 c_{12}^2 s_{12}^2 \sin^2\left(\frac{\Delta m_{12}^2}{4} \frac{L}{E}\right)$$

(2.17)

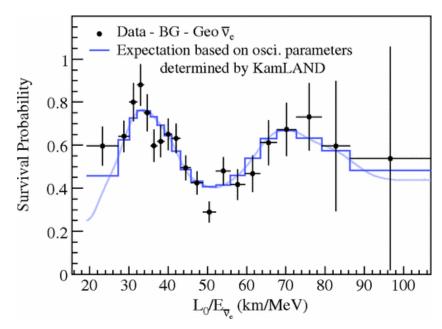

と反電子ニュートリノの観測確率が求められ、電子ニュートリノの検出量が sin 波の形で変動することが期待される。神岡鉱山内部にある液体シンチレーター検出器 KamLAND では、検出器から等距離にある原子炉より放出された反電子ニュートリノの検出が行われた。実験により得られた生存確率が図 2.1 である。この結果はニュートリノ振動現象が実際に生じている事を示しており、ニュートリノは非常に小さい質量を持つ事を示唆している。

図 2.1: KamLAND 実験にて観測されたニュートリノ振動 [2]。縦軸が反電子ニュートリノの生存確率、横軸が原子炉からの距離をニュートリノのエネルギーで割った L/E である。 $L_0=180km$  であり、反電子ニュートリノの生存確率が式 2.17 のように L/E に対して  $\sin$  波となっていることがわかる。

# 2.3.5 ニュートリノの質量階層構造

前章で述べたニュートリノ振動の観測によって、ニュートリノの振動パラメータについて現在が測定されている。しかし、ニュートリノ振動によって観測されるものはニュートリノ質量の二乗差であり、質量の絶対値及びそれらの大小関係については定める事ができない。したがって、得られたパラメータから考えられるニュートリノ質量の大小関係は以下の3通りあり、それぞれ順階層構造 (Normal Ordering)、逆階層構造 (Inverted Ordering)、準縮退構造 (Quasi Degenerate)と呼ばれる。

- 順階層構造

m<sub>1</sub> < m<sub>2</sub> ≪ m<sub>3</sub>

- 逆階層構造  $m_3 \ll m_1 < m_2$

- 準縮退構造  $m_1 \approx m_2 \approx m_3$

このニュートリノの質量階層構造はニュートリノの根本的な性質であり、構造の決定はニュートリノの物理において非常に重要なテーマであると言える。

| パラメータ                | 値                                   |     |

|----------------------|-------------------------------------|-----|

| $\sin^2 \theta_{12}$ | $0.307 \pm 0.013$                   |     |

| $\sin^2 \theta_{23}$ | $0.539 \pm 0.022$                   | 順階層 |

|                      | $0.546 \pm 0.021$                   | 逆階層 |

| $\sin^2 \theta_{13}$ | $(0.220 \pm 0.07) \times 10^{-2}$   |     |

| $\Delta m_{21}^2$    | $(7.53 \pm 0.18)^{-5}$              |     |

| $\Delta m_{32}^2$    | $(-2.536 \pm 0.034) \times 10^{-3}$ | 順階層 |

|                      | $(2.453 \pm 0.033) \times 10^{-3}$  | 逆階層 |

表 2.3: 測定されているニュートリノ振動パラメータ [3]

# 2.4 ニュートリノとマヨラナ粒子

# 2.4.1 ディラック質量とマヨラナ質量

## ディラック質量

自由ディラック場はラグランジアン密度を

$$\mathcal{L} = \bar{\psi}(i\partial \!\!\!/ - m_D)\psi \tag{2.18}$$

と表すことができる。ただし、 $m_D$  がディラック質量であり第二項目がディラック質量項である。 ラグランジアンはローレンツ不変かつエルミートであるため、これらの条件を満たすローレンツ スカラー  $\bar{\psi}\psi$  が質量項となる。ここで、場  $\psi$  について式 2.19 の射影演算子  $P_L, P_R$  を用いて式 2.20 のように右巻きと左巻きのカイラリティに分けることができる。

$$P_L = \frac{1}{2}(1 - \gamma_5) \qquad P_R = \frac{1}{2}(1 + \gamma_5) \tag{2.19}$$

$$\psi = \psi_L + \psi_R = P_L \psi + P_R \psi \tag{2.20}$$

また、

$$\bar{\psi}_{L,R} = (P_{L,R}\psi)^{\dagger}\gamma^0 = \psi^{\dagger}\gamma^0 P_{R,L} = \bar{\psi}P_{R,L}$$

(2.22)

を用いてディラック質量項を計算すると

$$m_D \bar{\psi} \psi = m_D (\bar{\psi}_L + \bar{\psi}_R) (\psi_L \psi_R) = m_D (\bar{\psi} P_R + \bar{\psi} P_L) (P_L \psi + P_R \psi)$$

=  $m_D (\bar{\psi}_L \psi_R + \bar{\psi}_R \psi_L)$  (2.23)

と書ける。

次に、反ニュートリノについて考える。反粒子は粒子の場に対する荷電共役に対応し、反ディラック場  $\psi^c$  は以下で与えられる。

$$\psi \xrightarrow{C} \psi^c \equiv C\psi C^- 1 = C\bar{\psi}^T \tag{2.24}$$

これを満たす変換 C は、以下のように与えられる。

$$C^{-1}\gamma_{\mu}C = -\gamma_{\mu}^{T}$$

$C^{-1}\gamma_{5}C = \gamma_{5}^{T}$   $C^{\dagger} = C^{-1} = C^{T} = -C$

これらを用いて、カイラリティごとの反ディラック場を計算すると、ディラック場の式を  ${\bf C}$  変換することで

$$P_{L,R}\psi = \psi_{L,R} \xrightarrow{C} P_{L,R}\psi^c = (\psi^c)_{L,R} = (\psi_{R,L})^c$$

(2.25)

と書け、反ディラック場のディラック質量項についても同様に

$$m_D \bar{\psi}^c \psi^c = m_D((\bar{\psi}^c)_L(\psi^c)_R + (\bar{\psi}^c)_R(\psi^c)_L)$$

(2.26)

と表される。

以上より、ニュートリノ及び反ニュートリノがそれぞれディラック質量を持つためには右巻きと左巻きの両方が存在しなくてはならない。しかし、Goldhaberの実験などからもわかるように、現在まで左巻きのニュートリノと右巻きの反ニュートリノしか発見されていない。よって、ニュートリノはディラック質量を持つことができず、ニュートリノ振動を説明することができない。

#### マヨラナ質量

前述の通り、ディラック質量を考えた場合にはニュートリノは質量を持つことができず、ニュートリノ振動を説明する事ができない。そこで、ニュートリノをマヨラナ粒子として扱うことで、左巻きのニュートリノと右巻きの反ニュートリノしか発見されていない現状においてもニュートリノに質量を与える事ができる。

マヨラナ粒子とは、粒子と反粒子が同一となる粒子のことである。ニュートリノはクォークおよびレプトンのなかで唯一電荷がゼロであることから、マヨラナ粒子であるとしても電荷に矛盾を生じない。

マヨラナ粒子は前述のように粒子と反粒子が同一であることから、

$$\psi = \psi^c \tag{2.27}$$

を満たす。このとき、ディラック質量項  $\bar{\psi}\psi$  以外にもローレンツ不変かつエルミートなスカラーを与える事ができる。具体的には、式 2.28 のように互いにエルミートな  $\bar{\psi}^c\psi,\bar{\psi}\psi^c$  を用いて式 2.29 のようにスカラー  $\mathcal{L}_M$  を構成する事ができる。

$$(\bar{\psi}\psi^c)^{\dagger} = (\psi^c)^{\dagger}(\psi^{\dagger}\gamma_0)^{\dagger} = (\psi^c)^{\dagger}\gamma_0\psi = (\bar{\psi}^c)\psi \tag{2.28}$$

$$\mathscr{L}_M = \frac{1}{2} (m_M \bar{\psi} \psi^c + m_M^* \bar{\psi}^c \psi) \tag{2.29}$$

これをマヨラナ質量項と呼び、 $m_M$  はマヨラナ質量である。先ほど得られたマヨラナ質量項についてカイラル演算子における右手系左手系のそれぞれで構成する事ができる。

$$\mathcal{L}^{L} = \frac{1}{2} m_L (\bar{\psi}_L \psi_R^c + \bar{\psi}_R^c \psi_L) = \frac{1}{2} m_L \bar{\psi}_L \psi_R^c + h.c.$$

(2.30)

$$\mathcal{L}^{R} = \frac{1}{2} m_{R} (\bar{\psi}_{R} \psi_{L}^{c} + \bar{\psi}_{L}^{c} \psi_{R}) = \frac{1}{2} m_{R} \bar{\psi}_{L}^{c} \psi_{R} + h.c.$$

(2.31)

## 2.4.2 シーソー機構

前章の議論を用いて、ディラック質量項とマヨラナ質量項両方を合わせたラグランジアンは

$$2\mathcal{L} = m_D(\bar{\psi}_L\psi_R + \bar{\psi}_L^c\psi_R^c) + m_L\bar{\psi}_L\psi_R^c + m_R\bar{\psi}_L^c\psi_R + h.c.$$

$$= (\bar{\psi}_L, \bar{\psi}_L^c) \begin{pmatrix} m_L & m_D \\ m_D & m_R \end{pmatrix} \begin{pmatrix} \psi_R^c \\ \psi_R \end{pmatrix} + h.c. = \bar{\Psi}_L M \Psi_R^c + \bar{\Psi}_R^c M \Psi_L$$

(2.32)

のように書ける。ただし、スピノル $\,\Psi_L,\Psi^c_R\,$ は以下を用いた。

$$\Psi_L = \begin{pmatrix} \psi_L \\ \psi_L^c \end{pmatrix} = \begin{pmatrix} \psi_L \\ (\psi_R)^c \end{pmatrix} \qquad (\Psi_L)^c = \begin{pmatrix} (\psi_L)^c \\ \psi_R \end{pmatrix} = \begin{pmatrix} \psi_R^c \\ \psi_R \end{pmatrix} = \Psi_R^c \qquad (2.33)$$

式 2.32 の行列 M を質量行列と呼び、これを対角化することで以下のように質量固有状態の質量  $m_1, m_2$  が求められる。

$$m_{1,2} = \frac{1}{2} \left[ (m_L + m_R) \pm \sqrt{(m_L - m_R)^2 + 4m_D^2} \right] = m_{\nu,N}$$

(2.34)

この二つの質量固有状態のうち  $m_{\nu}$  は非常に軽く現在まで観測されている  $\nu_L$ ,  $\bar{\nu}_R$  に対応する。  $m_N$  については未発見のニュートリノ  $N_R$ ,  $\bar{N}_L$  とし、式 2.35 のように質量が非常に大きいと仮定する。この時、 $m_{\nu}$  は式 2.36 のように表され、 $m_D$  と比べて非常に小さくなる事がわかる。

$$m_D \ll m_N \tag{2.35}$$

$$m_{\nu} = \frac{m_{nu}m_N}{m_N} \simeq \frac{m_D^2}{m_N} \ll m_D \tag{2.36}$$

以上の議論のように、ニュートリノがマヨラナ粒子である時、未発見の右巻きニュートリノの質量が非常に大きいと仮定することでニュートリノの質量を非常に小さくする事ができる。この過程をシーソー機構と呼び、右巻きニュートリノが未発見であることや左巻きニュートリノの質量が小さい理由を説明する事ができることから、さまざまな実験によって検証が進められている。

# 2.5 ニュートリノを伴わない二重ベータ崩壊によるマヨラナ性の検証

ベータ崩壊は式 2.1 のように原子核中の中性子が陽子と電子、反電子ニュートリノに崩壊する 反応である。ベータ崩壊前後の原子について、その質量は Weizsacker の式 (式 2.37)

$$m(Z, A = const.) \propto const. + \alpha Z + \beta Z^2 + \delta_p$$

(2.37)

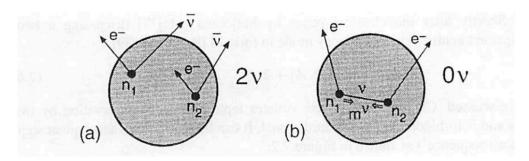

図 2.2: 二重ベータ崩壊の概略図 [4]。左が  $2\nu\beta\beta$ 、右が  $0\nu\beta\beta$  崩壊である。

で表される。ここで、 $\delta_P$  の項は対エネルギー項であり、以下のように原子核の陽子と中性子の数によって決定される。

$$\delta_P = \begin{cases} -a_P A^{-1/2} & 偶偶核 \\ 0 & 偶奇核または奇偶核 \\ +a_P A^{-1/2} & 奇奇核 \end{cases}$$

(2.38)

よって、質量数 A が偶数の時、以下の条件を満たす原子核が存在する。

$$\begin{cases}

m(Z, A) < m(Z + 1, A) \\

m(Z, A) > m(Z + 2, A)

\end{cases}$$

(2.39)

この原子核においては m(Z,A) から m(Z+1,A) の崩壊が禁止され、式 2.40 のようにニュートリノを伴う二重ベータ崩壊  $(2\nu\beta\beta$  崩壊) が生じる。

$$(Z, A) \to (Z + 2, A) + 2e^- + 2\bar{\nu}_e$$

(2.40)

また、ニュートリノがマヨラナ性を持つとき図 2.2 のようにニュートリノを伴わない二重ベータ 崩壊  $(0\nu\beta\beta$  崩壊) が可能であり、その反応は式 2.41 のように表される。

$$(Z, A) \to (Z + 2, A) + 2e^-$$

(2.41)

この反応ではニュートリノがエネルギーを持ち去らないことから、電子が崩壊時の全エネルギーを持ち、エネルギースペクトルにおいて  $\mathbf{Q}$  値付近の鋭いピークとして観測される。 $0\nu\beta\beta$  崩壊が観測されればニュートリノがマヨラナ性を持つことを示す事ができる。

$0

u\beta\beta$  崩壊の半減期は有効マヨラナ質量によって表され

$$T_{1/2}^{0\nu} = (G_{0\nu}|M_{0\nu}^2|\langle m_{\beta\beta}\rangle)^{-1}$$

(2.42)

という関係を持つ。よって、 $0\nu\beta\beta$  崩壊を観測する事ができれば半減期によりニュートリノのマヨラナ質量を制限する事ができる。

# 第3章

# KamLAND

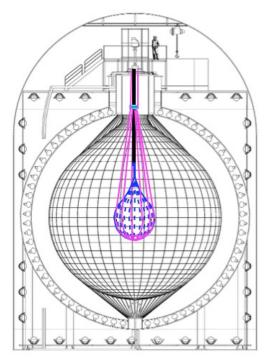

KamLAND は液体シンチレーター検出器であり、ニュートリノの検出を目的として 2002 年から稼働を開始した。この章では、KamLAND 検出器の概要及び KamLAND-Zen 実験の概要を説明し、今後建設予定である次世代検出器 KamLAND2 について説明する。

# 3.1 液体シンチレーター検出器 KamLAND

# 3.1.1 KamLAND の概要

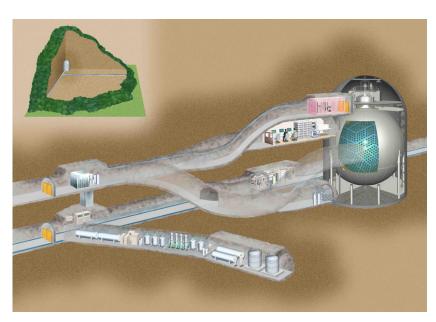

KamLAND は岐阜県飛騨市にある池ノ山の地下 1,000 m の KamiokaNDE 検出器跡地に建設された大型液体シンチレーター検出器である。主な検出対象は反電子ニュートリノであり、地下への建設による宇宙線ミューオンの低減や極低放射能環境の実現によって高感度観測が可能である。 KamLAND は原子炉がおおよそ等距離にある立地を生かし、原子炉ニュートリノ振動の観測を

図 3.1: 池の山地下に建設された KamLAND

14 第 3 章 KamLAND

図 3.2: KamLAND の内部構造。内部検出器を赤、外部検出器を青色で示した。

行った。結果として、図 2.1 のように原子炉ニュートリノ振動の二周期にわたる観測に成功した。

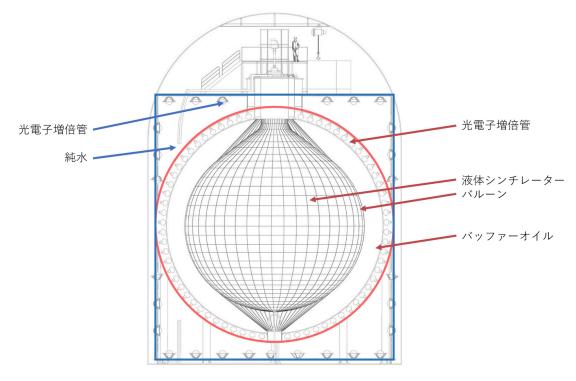

# 3.1.2 KamLAND の構造

KamLAND 検出器の構造を図 3.2 に示す。KamLAND は内部と外部の二層構造となっている。 内側は球形のシンチレーション検出器となっており (内部検出器)、その外部は純水で満たされて おり水チェレンコフ検出器の役割を果たす (外部検出器)。

#### 内部検出器

内部検出器は球形ステンレスタンク内部を指し、液体シンチレーターの入った直径 13 m のバルーンおよび光電子増倍管、バッファーオイルによって構成されるシンチレーション検出器である。

ニュートリノの逆ベータ崩壊をはじめとするバルーン内部で生じたさまざまな物理現象によって生じた荷電粒子が液体シンチレーターの分子を励起し、それが脱励起する際にシンチレーション光を放出する。こうして放出されたシンチレーション光を光電子増倍管によって検出する事でイベントの観測を行う。

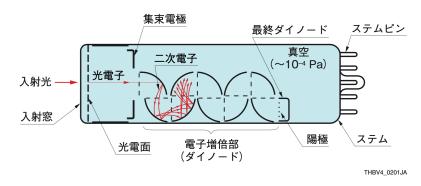

図 3.3: PMT の内部構造 [5]。図中のダイノードはラインフォーカス型である。

## 外部検出器

外部検出器は、KamLAND の最外部の円筒形タンクと球形ステンレスタンクの間の領域を指し、ここを満たす純水と円筒形タンク壁面に取り付けられた光電子増倍管によって構成される。

外部から飛来した粒子が水中に入射した際に生じるチェレンコフ光の検出を行なっており、主 な観測対象は宇宙線ミューオンである。

#### 光電子増倍管

光電子増倍管 (PMT) は、光電効果を用いて微弱な光を検出する高感度な光センサーである。

PMT の構造を図 3.3 に示す。PMT の光電面に光子が入射すると、光子の衝突によって電子が叩き出される (光電効果)。その後、こうして叩き出された電子 (光電子) が電子増倍部によって増幅され、検出可能な大きさの電気信号として陽極から出力される。

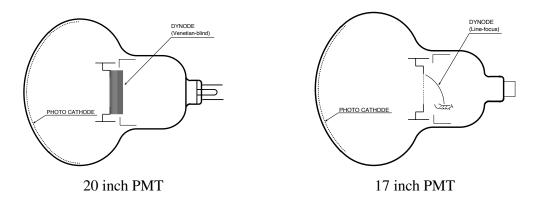

KamLAND では、図 3.4 のような浜松ホトニクス社製の 17 inchPMT 及び 20 inchPMT が使用されている。20inchPMT はベネチアンブラインド型のダイノードを持ち、KamiokaNDE 検出器より利用されてきた PMT を改修したものである。17 inchPMT はボックス型とラインフォーカス型のダイノードを持ち、KamLAND 用に開発された PMT である。また、17 inchPMT の外径は 20 inch であるが、入射窓の一部を覆うことで分解能の良い直径 17 inch 分のみを利用しているためこのように呼ばれる。

### 液体シンチレーター

液体シンチレーターは、荷電粒子との反応等によって励起し脱励起の際に発光する液体である。 (シンチレーション光)。 KamLAND では表 3.1 に示す組成の液体シンチレーターが用いられており、これを Kam-LS と呼ぶ。

#### バッファーオイル

バッファーオイルは、PMTと液体シンチレータの間を満たす液体である。バッファーオイルの成分を表 3.2 に示す。バッファーオイルの役割は、PMT及びステンレスタンクの原料に混入して

16 第 3 章 KamLAND

図 3.4: KamLAND で使用されている PMT の外形図

成分 化学式 密度 体積比 備考 ドデカン  $C_{12}H_{26}$ 0.7526 80.2 % 密度調整及び透過率の低下防止 プソイドクメン  $C_9H_{12}$ 0.8796 19.8% 溶媒 PPO  $C_{15}H_{11}NO$ 発光剤, 濃度は 1.36 g/L

表 3.1: Kam-LS の成分表

表 3.2: バッファーオイルの成分表

| 成分      | 化学式            | 体積比 |

|---------|----------------|-----|

| ドデカン    | $C_{12}H_{26}$ | 53% |

| イソパラフィン | $C_nH_{2n+2}$  | 47% |

いる放射性元素から出る放射線の液体シンチレーターへの入射を遮る役割を持つ。

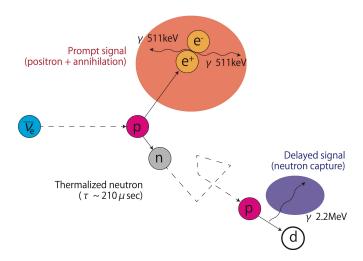

## 3.1.3 ニュートリノの検出原理

KamLAND によるニュートリノの検出原理は二種に分ける事ができる。逆ベータ崩壊を用いた 検出と電子散乱反応による検出である。

## 逆ベータ崩壊による反電子ニュートリノの検出

KamLANDでは、逆ベータ崩壊を用いることで反電子ニュートリノの検出が可能となっている。逆ベータ崩壊は液体シンチレーター中の中性子と反電子ニュートリノによって起こり、式 3.1 で表される。

$$\bar{\nu}_{\rm e} + {\rm p} \rightarrow {\rm e}^+ + {\rm n}$$

(3.1)

逆ベータ崩壊反応とその後に生じる信号の様子を図 3.5 に示す。反電子ニュートリノが逆ベータ崩壊を起こした際に陽電子と中性子が生じる。その後、陽電子については液体シンチレーター中の電子と対消滅を起こし、511 keV のガンマ線を 2 つ放出する (先発信号)。中性子については、

図 3.5: 逆ベータ崩壊反応。陽電子の対消滅と中性子の捕獲時にそれぞれ 511keV、2.2MeV の信号が生じる。

およそ 210  $\mu$ sec 後に液体シンチレーター中の水素によって捕獲されることで 2.2 MeV のガンマ線を放出する (後発信号)。このように、逆ベータ崩壊反応によって 511 keV の二つの先発信号と 210  $\mu$ sec 後に検出される 2.2 MeV の後発信号を生じるため、遅延同時計測法によって反電子ニュートリノの検出が可能となっている。

## 電子散乱によるニュートリノの検出

KamLANDでは、電子散乱による信号を観測することで、すべてのフレーバーのニュートリノ及び反ニュートリノについて検出がなされる。電子散乱は

$$\nu + e \to \nu + e \tag{3.2}$$

と表される反応である。これは弱い相互作用による反応であり、中性カレント反応と荷電カレント反応の二種類存在する。中性カレント反応による散乱では、すべてのフレーバーのニュートリノが電子との散乱が可能である。荷電カレント反応による反応は、電子ニュートリノ及び反電子ニュートリノによってのみ生じる。よって、電子散乱によるニュートリノの検出では電子フレーバーのニュートリノの散乱弾面積が最も大きくなる。

# 3.2 KamLAND-Zen 実験

KamLAND-Zen 実験は KamLAND にミニバルーン及びキセノン含有液体シンチレーターを新たに導入し、 $^{136}$ Xe による  $0\nu\beta\beta$  崩壊の探索を行う実験である。本実験は 2011 年に開始し、2024 年に終了している。開始から終了までの期間には使用するキセノン量を増やすアップデートを行っており、使用したキセノンの量によって KamLAND-Zen 400 及び KamLAND-Zen 800 と二つの期間に分けられている。

第3章 KamLAND

| 成分      | 化学式              | 密度     | 体積比   | 備考                |

|---------|------------------|--------|-------|-------------------|

| デカン     | $C_{12}H_{26}$   | 0.735  | 82.4% | 密度調整を考慮           |

| プソイドクメン | $C_{9}H_{12}$    | 0.8796 | 17.6% | 溶媒                |

| キセノン    | $C_{15}H_{11}NO$ | -      | -     | 発光剤, 濃度は 1.36 g/L |

表 3.3: Xe-LS の成分表

# 3.2.1 KamLAND-Zen 実験における検出器の構造

KamLAND-Zen 実験における KamLAND 検出器のセットアップを図 3.6 に示す。

図 3.2 の KamLAND 検出器と異なり、検出器中央新たにミニバルーンが搭載されているのが特徴である。

ミニバルーンをインストールした KamLAND

KamLAND に導入されたミニバルーン

図 3.6: KamLAND-Zen 実験で使用された検出器のセットアップ

ミニバルーンは Xe 含有液体シンチレーター (Xe-LS) によって満たされており、ミニバルーン内で  $0\nu\beta\beta$  崩壊が生じた際に、内部検出器にてイベントの検出を行うためのセットアップとなっている。Xe-LS の成分表を表 3.3 に示す。

図 3.7: KamLAND-Zen800 によって得られたエネルギースペクトル [1]

# 3.2.2 KamLAND-Zen 400

KamLAND-Zen 実験として最初に行われたのが、KamLAND-Zen 400 である。KamLAND-Zen 400 は Phase I と Phase II に分けられ、Phase II は Phase I の観測で検出された <sup>110m</sup>Ag によるバックグラウンドを大幅に減少した。

この Phase I 及び Phase II の結果をまとめることで、 $0\nu\beta\beta$  崩壊の寿命に対し

$$T_{0\nu\beta\beta}^{1/2} > 1.07 \times 10^{26} \text{year}(90\%\text{C.L.})$$

(3.3)

という制限を与えた [6]。

# 3.2.3 KamLAND-Zen 800

KamLAND-Zen 400 からアップデートを加えた実験が KamLAND-Zen 800 である。 KamLAND-Zen 800 では Xe 量を増加しており、約 745 kg が使用された。本実験は 2024 年に終了しておりこの結果と KamLAND-Zen 400 の結果と合わせることで、 $0\nu\beta\beta$  崩壊の寿命に対し

$$T_{0\nu\beta\beta}^{1/2} > 3.8 \times 10^{26} \text{year}(90\%\text{C.L.})$$

(3.4)

という制限を与えた [1]。KamLAND-Zen 800 によって得られたエネルギースペクトルを図 3.7 に示す。

# 3.2.4 KamLAND-Zen 実験における主な背景事象

KamLAND-Zen 実験で観測されていた主な背景事象として、以下が挙げられる。

#### ミューオン核破砕によって生成される不安定核の崩壊

宇宙線ミューオンは宇宙から飛来する高エネルギーな  $\mu$  粒子である。KamLAND は池ノ山地下 1,000 m に建設することで、その地盤の厚さによりこの宇宙線ミューオンによるイベントを 10万分の 1 にまで減少しているが、その影響は無視することができずおよそ 0.3 Hz ほどでイベントが観測されている。

宇宙線ミューオンはミューオンが液体シンチレーター中の  $^{12}$ C や  $^{136}$ Xe 原子核を破砕し不安定核を生成する。この不安定核は崩壊時に中性子を放出し、これがバックグラウンドとなる。この過程は C の核破砕によるものと Xe の核破砕によるものに分けられる。

$^{12}$ C 原子核の破砕によっては  $^{10}$ C などの不安定核が生成し、寿命は長いもので数 10 秒程度である。これらの崩壊事象の除去には遅延同時計測が用いられている。

Xe 原子核の破砕では長寿命な不安定核の生成が多く、遅延同時計測による背景事象の除去が難しい。そこで、中性子イベントと宇宙線ミューオン情報などを用いた見積もりによって背景事象の除去を行なっている。この背景事象除去の精度向上のためには、中性子検出効率の向上が必要である。

### インナーバルーン付近における <sup>214</sup>Bi の崩壊

$^{214}$ Bi は  $^{238}$ U 系列の放射性元素であり、その崩壊時に生じる Q 値 3.27 MeV の  $\beta$  崩壊が背景事象として観測される。これの排除には、その娘核である  $^{214}$ Po が起こす  $\alpha$  崩壊の観測による遅延同時計測が望ましい。しかし、ここで放出される  $\alpha$  線がバルーンに衝突した場合、エネルギーが大きく減少し検出効率が下がる。これを防ぐため、シンチレーションバルーンの導入が検討されている。

#### $^{136}$ Xe の $2\nu\beta\beta$ 崩壊

本研究において  $0\nu\beta\beta$  崩壊核として使用している  $^{136}$ Xe は他に  $2\nu\beta\beta$  崩壊の経路をもつ。 $0\nu\beta\beta$  はニュートリノを生じない反応であることからエネルギーが鋭いピークを持ち、反対に  $2\nu\beta\beta$  はニュートリノが持ち去るエネルギーによってスペクトルに広がりを持つ。

実際の検出器においてはエネルギー分解能が有限であることから、 $0\nu\beta\beta$  についてもスペクトルが広がりを持つ。これにより、実際の検出では両者のスペクトルが重なってしまい、 $2\nu\beta\beta$  が背景事象となる。この背景事象を減少させるには、検出器のエネルギー分解能を向上することで  $0\nu\beta\beta$  のスペクトルをシャープにする必要がある。

#### 3.2.5 KamLAND2

KamLAND-Zen 800 実験を終えて、KamLAND 検出器に更なるアップデートを加えた KamLAND2 検出器の建設とそれを用いた KamLAND2-Zen 実験が計画されている。KamLAND2 検出器は各部にアップデートを加え、更なるエネルギー分解能の向上を目指している。主な各部のアップデートは以下の通りである。

- 新型データ収集システム フロントエンド回路に搭載された大容量バッファによる中性子検出効率の向上

- シンチレーションバルーン  $\alpha \ \, \text{線によってバルーンが発光することで、従来では検出できなかったバルーン表面での Po} \\ \ \, 崩壊イベントを検出$

- 集光ミラー シンチレーション光を効率よく PMT に集めることで検出効率を向上

- 液体シンチレーターの改良 発光の波長変換剤 Bis-MSB の導入により、シンチレーションバルーンの発光を区別

- 高量子効率 PMT PMT の改良により発光の検出感度が向上

# 第4章

# KamLAND のデータ収集システムにお けるトリガーシステム

KamLAND におけるデータ収集システムは図 4.1 のような体系にて構築されており、KamLAND 建設当初より使用されている KamDAQ と 2010 年に新たに導入された MoGDAQ の二系 統に分かれている。

図 4.1: KamLAND のデータ DAQ 全体像 [7]

図 4.2: KamFEE のボード外見写真 (左) と実装部品の配置図 (右)[8]

# 4.1 KamDAQ

KamDAQ はトリガーボードから発行された波形取得コマンドに基づきフロントエンド電子回路 (以下 KamFEE) によって PMT 信号の取得を行い、VMEbus を通じて解析用 PC に送信する。以下では、DAQ を構築する電子回路それぞれについて解説する。

## 4.1.1 KamFEE

KamDAQ では、KamFEE と呼ばれるフロントエンド電子回路によって PMT 波形のデジタイズ及び波形送信を行っている。KamFEE の基盤外見図を図 4.2 に示す。KamFEE は操作及び信号送受信のための VMEbus と PMT 信号入力用に 12 チャンネルのポートによって信号の入出力を行う。KamFEE にはそのほか、信号のデジタイズに用いる Analog Transient Waveform Degitizer (ATWD) や FPGA、波形データ保持のためのメモリが搭載されている。

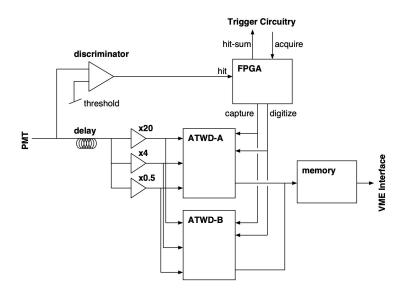

KamFEE による信号処理のブロックダイアグラムを図 4.3 に示す。KamFEE に入力した PMT 信号は、ヒット判定の回路とデジタイズの回路に分配される。ヒット判定では、入力信号に対しディスクリミネーターによる閾値判定ののち、FPGA によってヒットチャンネルの数 (nhits) が外部へ出力される。

デジタイズでは、入力信号を 0.5、1、20 倍で増幅し (L、M、H-gain)、入力波形に応じたレンジの信号を選択しデジタイズしている。このように、複数の増幅率の信号を用いることで低電圧信号では ATWD の 2 倍のレンジによる波形の取得が可能となっている。

ATWD はコンデンサアレイによるアナログ信号の保持を行っており、波形取得コマンドが入力した際に ADC によってデジタイズを行っている。デジタイズには約 25  $\mu$ s の時間がかかり、これがデッドタイムにつながる。そこで、KamFEE では 2 つの ATWD を交互に使用する事でこのデッドタイムの発生を軽減している。

図 4.3: KamFEE のブロックダイアグラム [8]

#### 4.1.2 トリガー

トリガー回路は、波形取得コマンドを発行する役割を持つ。トリガー回路は全 KamFEE と接続されており、KamFEE に対し GPS と同期した 40 MHz クロックの供給やトリガーコマンドの入力を行っている。

トリガーコマンドについては、KamFEE からの Hit 情報の総和である NSUM を元に波形取得コマンドを発行するほか、NSUM の推移を確認する History トリガーやキャリブレーショントリガーなど 20 種類以上のトリガーコマンドが存在する。

#### 4.1.3 DAQ コンピューター

DAQ コンピューターは KamFEE ボードからのデータ取得を行うフロントエンド PC とオンライン解析やデータストレージ等を担うバックエンド PC からなる。

フロントエンド PC は KamFEE と光ファイバーにて接続されており、通信によって KamFEE へ電気的なノイズを与えないよう設計されている。バックエンド PC は、オンライン解析用 PC、データ保存用 PC、システムコントロール用の PC から構成される。

# 4.2 KamDAQ のデッドタイムとミューオン信号

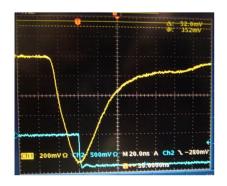

ミューオンによる PMT 信号が KamDAQ によって観測される際におよそ 1 msec の間 1p.e. 程度の信号に対する検出感度が低下する。原因は、ミューオン信号直後の波形に見られるオーバーシュート及びアフターパルスである。典型的なミューオン信号とミューオン信号直後の PMT 信号を図 4.4 に示す。

図 4.4: ミューオン信号 (左) と直後に見られるオーバーシュート及びアフターパルス (右)[9]

図 4.5: PMT のブリーダ回路 [10]

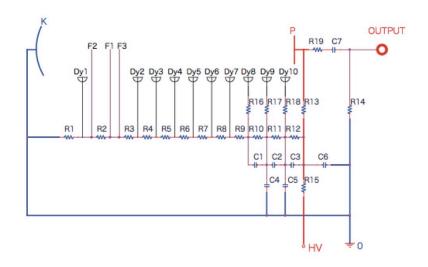

#### 4.2.1 オーバーシュート

オーバーシュートは大光量なミューオン信号が PMT によって観測されることによって生じる。 図 4.5 に PMT のブリーダ回路図を示す。このブリーダ回路にて大電流を伴うミューオン信号が AC カップルされる際に、カップリングコンデンサ (図 4.5 中 C7) が充電される。その後、ミューオン信号による電流が流れ終わった際にコンデンサの放電が起こり、抵抗 (図 4.5 中 R14) に正電圧が生じる。この現象は通常の信号においても生じるが、その効果は非常に小さく、無視する事ができる。

ミューオンによるオーバーシュートはベースラインの正方向への約  $1\,\mathrm{mV}$  の変動という形で PMT 波形に影響を与え、ベースライン回復には約  $1\,\mathrm{msec}$  を要する。これにより、 $1\mathrm{p.e.}$  程度の PMT 波形はベースライン変動を受けた結果 KamFEE の Hit 閾値を超える事ができなくなる。このようにして KamFEE にオーバーシュートによるデッドタイムが生じる。

4.3 MoGDAQ 27

#### 4.2.2 アフターパルス

ミューオン入射時には二つの過程によってアフターパルスが生じる。一つ目は、ダイノードの電子の弾性散乱である。この成分は信号直後に大きな負電圧が見える事が特徴である。二つ目は、PMT 内部の残留ガスの電離作用である。この成分は数  $\mu$ s にも渡り高レートな信号をもたらし、KamFEE のデジタイズ速度を超えることで、デッドタイムをもたらす。

#### 4.2.3 ミューオン核破砕反応による長寿命原子核

ミューオンは入射時の信号のオーバーシュート、アフターパルスによってデッドタイムをもたらすだけでなく、液体シンチレーター中の C や Xe 原子核の破砕によって長寿命な不安定核を生成する。この不安定核の崩壊によって中性子捕獲の背景事象を生じる。

KamLAND ではこの中性子の検出情報を用いた不安定核のタグが行われているが、旧トリガーシステムにおいては 4.3.4 章で説明するように中性子検出効率の低下が課題となっている。 KamLAND2 ではトリガーシステムの刷新により課題の解決が期待されており、その詳細は 5.1章で説明する。

#### 4.3 MoGDAQ

MoGDAQ は 2010 年に運用が開始されたデータ収集システムで、運用開始後は KamFEE と並行して稼働していた。MoGDAQ は BLR、MoGURA FADC、Piggy-back、MoGURA trigger によって構成されている。

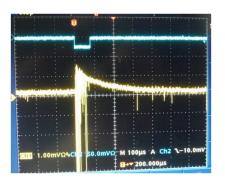

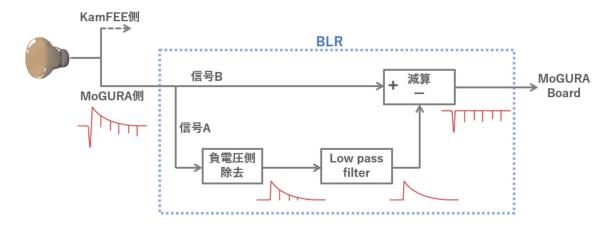

#### 4.3.1 BLR

Baseline Restorer (BLR) はアナログ回路を用いて、ミューオン信号による PMT 波形のオーバーシュートの除去を行う機能を持つ。BLR によって KamFEE の課題であったオーバーシュートによるデッドタイムの解消を達成している。

図 4.6 に BLR の信号処理概略を示す。BLR では、負電圧の信号除去及びローパスフィルタによってオーバーシュートによるベースライン変動分の波形を取り出す。その後、元信号からベースライン変動波形を差し引くことで、ベースラインを回復する。

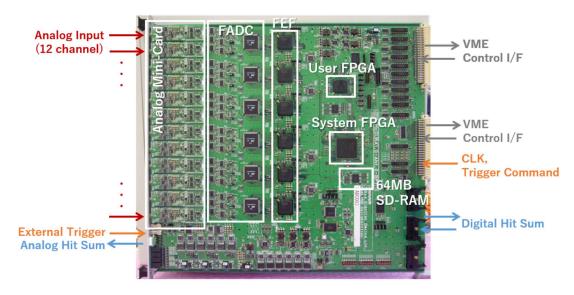

#### 4.3.2 MoGURA

KamFEE における課題点であったデジタイズに要するデッドタイムを解決するために開発されたフロントエンド回路が Module for General-Use Rapid Application (MoGURA) である。 MoGURA はデッドタイムフリーな波形取得を目的として作成されており、KamFEE の課題であったデータ取得の際に生じるデッドタイムを大幅に削減している。

MoGURA の基盤外見図を図 4.7 に示す。MoGURA は 12 チャンネルの BNC 入力をもち、12

図 4.6: ミューオン信号に対する BLR 処理の概略図 [11]

図 4.7: MoGURA ボードと主な実装部品 [11]

本の PMT 波形の取得が可能である。そのほか波形処理を行うアナログ回路、デジタイズを行う FADC、データフレームを作成する Front End FPGA、データ送受信を行う System-FPGA、データ保存用 SD-RAM が実装されている。これらの実装部品によって処理された波形データ及び ヒット本数情報などは VME バスによって出力される。

#### **FADC**

BLR によってベースライン回復がなされた PMT 波形を分岐し、それぞれ異なる増幅率にて増幅したのちにデジタイズを行うことで、4 種類の分解能及びレンジによるデジタイズを実現する。 MoGURA における各ゲインチャンネルのデジタイズ性能を表 4.1 に示す。

FADC のデジタイズは 1 クロックで完了するため、KamFEE において課題となっていた波形の デジタイズ時間に起因するデッドタイムが大きく削減されている。 4.3 MoGDAQ **29**

| ゲインチャンネル        | P-gain               | H-gain               | M-gain           | L-gain          |

|-----------------|----------------------|----------------------|------------------|-----------------|

| ダイナミックレンジ [V]   | $+0.005 \sim -0.020$ | $+0.025 \sim -0.100$ | $+0.250 \sim -1$ | $+2.5 \sim -10$ |

| 分解能 [mV]        | 0.1                  | 0.5                  | 5                | 50              |

| サンプリングレート [GHz] | 1                    | 0.200                | 0.200            | 0.200           |

| 増幅率             | ×120                 | ×24                  | ×2.4             | ×0.24           |

表 4.1: MoGURA の各ゲインチャンネル [11]

#### Frontend FPGA (FEF)

MoGURA ボード 1 枚につき 6 枚搭載されており、FEF あたり 2 チャンネルの波形処理を行う。主な機能はヒット判定と波形取得時間情報の保持および波形バッファリングである。

#### System FPGA

System FPGA では、波形取得コマンドの入力時に FEF からデータ読み出しを行い、外部とのデータ通信を行う。主な通信はデイジーチェーン接続による Hitsum の加算及びトリガーマンド入力時の波形送信である。

#### 4.3.3 MoGURA trigger

MoGURA trigger は MoGURA に対し波形取得コマンドを発行する役割を持つ。波形取得コマンドはコマンドとコマンドフラグからなる。

波形取得コマンドに用いるコマンドを以下に示す。

#### • Acquire-Range

一定長の全波形をを取得する。取得する波形の長さを EventWindow と呼ぶ。

#### • Acquire-Hit

Hit のない波形やサチレーションを起こしている波形を除いた波形を取得する (ゼロサプレッション)。

波形取得におけるコマンドフラグのうち主要なものを以下に示す。

#### • Single Trigger

通常のイベント検出を目的としたフラグ。Nhit の値が Single Threshold と呼ばれる閾値を超える場合に発行されたトリガーに付与される。ここで、Nhit は Hitsum を Hit Window の期間だけ累積した値であり、検出器の大きさと全発光の PMT への到達時間を光量し HitWindow は 120 ns に設定されている。

#### Prescaled Trigger

トリガーレートを落とすことを目的としたフラグ。Hit Window 期間による Nhit の算出を 指定時間ずつ間引くことで、トリガーレートを減らすことを目的としている。

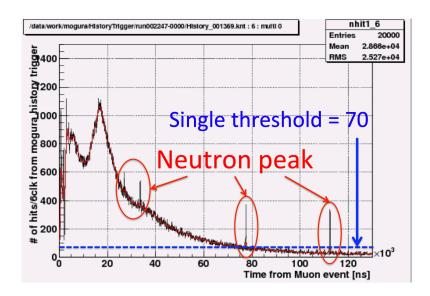

図 4.8: ミューオン信号後の NHit 分布 [10]。赤丸で囲まれた NHit のピークが中性子捕獲事象によるものである。

#### • Launch Trigger

宇宙線ミューオンへの対応を目的としたフラグ。Nhit の閾値が Single Trigger のものより高く設定されている。

#### Adaptive Trigger

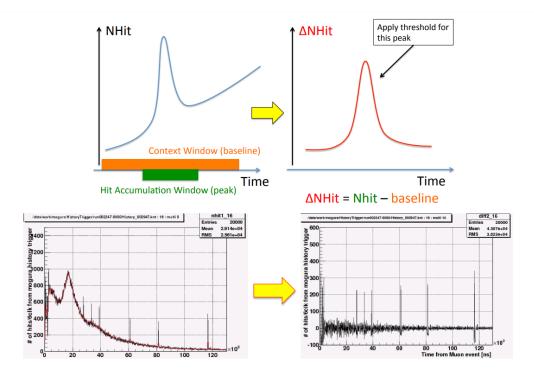

ミューオン信号後の中性子捕獲事象の検出を目的としたフラグ。ミューオン後はノイズによる信号が多く、図 4.8 のように NHit のベースラインが大きく変動する。そこで、その間 NHit そのものの大きさではなくベースラインとの差分を取った  $\Delta$ NHit に対する閾値判定によって発行される。 $\Delta$ NHit は図 4.9 のように Nhit から Context Window によってよって算出された Nhit ベースラインを差し引くことで中性子による Nhit のピークを検出する。

#### • PPS Trigger

1 sec 間隔で発行され、定期的な波形取得を行う。

• Baseline Trigger

任意の時間間隔で発行され、全チャンネルの波形を取得する。

#### 4.3.4 現行 MoGDAQ の課題点

MoGDAQ は KamFEE の課題点を克服したものとなっているが、運用上において以下のような課題点が存在する。

#### Hitsum 算出の取り扱いが不便であること

MoGDAQ の課題点として、Hitsum 算出の取り扱いが不便であることがあげられる。 MoGDAQ では全 MoGURA の Hitsum の加算を行うために、デイジーチェーン方式による接 4.3 MoGDAQ 31

図 4.9:  $\Delta$ NHit の算出 [10]。NHit からベースラインを差し引くことで中性子のピークが検出されている。

続を行っている。デイジーチェーン接続では全 MoGURA の Hitsum ケーブルを数珠繋ぎにすることで、隣のボードから MoGURA ボード入力された Hitsum に対して自分自身が持つ Hitsum を加算し次のボードへ送り出すという動作を行う。

Hitsum の伝達経路に着目すると全てのボードが直線上に接続されているため、MoGURA ボードに故障が見られた場合、そのボードから先の Hitsum については加算することが出来ないという欠点がある。よって、1 枚のボードの故障が Hitsum 算出全体に影響を及ぼすため早急なボード交換が必要となるほか、Hitsum ケーブルの取り扱いが不便である現状がある。

#### オンボードメモリの容量不足による中性子検出効率の低下

MoGURA はデッドタイムフリーなデータ収集を目指したエレクトロニクスであり、信号のデジタイズにおいてはこれを達成している。しかし、デジタイズ後波形を保持するために各 MoGURA に実装されているメモリ (以下オンボードメモリ) については容量が不足している問題があった。

オンボードメモリ容量の不足は、図 4.10 のようなミューオンイベント直後の中性子検出効率の低下をもたらすほか、メモリがフルになった際には DAQ のクラッシュを引き起こす。中性子の検出はミューオンによる不安定核のイベントのタグに用いられており、中性子検出効率の低下はタグ効率の低下を招くことから大きな課題となっている。

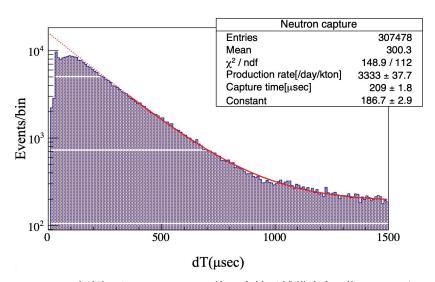

図 4.10: MoGDAQ にて観測されたミューオン後の中性子捕獲事象 (紫ヒストグラム) と不安定核種の寿命によりフィットした中性子捕獲事象数 (赤)[12]。ミューオン後約  $100\mu s$  は観測量が少なく、MoGDAQ では全中性子が捕獲されていないと考えられる。

#### 近傍超新星爆発への対応

超新星爆発では恒星内部での核融合によって多量の超新星ニュートリノが放出される。Kam-LANDではベテルギウスをはじめとする近傍超新星による超新星ニュートリノについても検出が可能となっている。しかし、そのイベントレートは非常に大きく、MoGURAのバッファサイズ及びデータ処理速度の制約によりすべてのイベントを満足に取得することは不可能であった。

# 第5章

# KamLAND2 におけるトリガーシステムの概要

トリガーシステムとは、PMT の波形観測及び発光事象の選定及び送信を行うシステムである。より詳細には、トリガーシステムのフロントエンド電子回路 (以下 FEE) によって PMT の波形観測を行いそれが発光信号であるかどうか判定をする (以下ヒット判定)。ここで発光信号が見られた PMT の状態をヒットと呼び、ヒットしている PMT の数をヒット本数などと呼ぶ。その後、ヒット PMT の波形についてそれが物理イベントによる発光であるかの判定を行う (以下イベント検出)。その後、物理イベントであると判定された場合にはトリガーコマンドとよばれる信号を発行することで FEE による観測波形の記録及び送信を行う。

KamLAND2のトリガーシステムは従来のものから刷新することによって宇宙線ミューオンによる不安定核のタグ効率に大きく影響する中性子検出効率の改善が期待されている。本章では、KamLAND2へ導入予定となっているトリガーシステムの全体像及びその動作について説明する。はじめに従来の MoGDAQのトリガーシステム(旧トリガーシステム)における課題点を踏まえ、これらの解消を目指した KamLAND2のトリガーシステムへの要求について整理する。その後、トリガーシステムの導入計画及び具体的なトリガーシステムの概要を説明する。

# 5.1 トリガーシステムへの要求

本項目では、トリガーシステムへの要求を旧トリガーシステムの課題点を踏まえて説明する。 トリガーシステムへの要求として以下の4点が挙げられる。

#### 中性子検出効率を改善すること

旧トリガーシステムの課題点となっていたオンボードメモリの容量不足による中性子検出効率の制限について、トリガーシステムに使用する FEE の性能向上によって解決を目指す。表 5.1 に旧トリガーシステムとトリガーシステムの FEE が備えるオンボードメモリ容量を示す。旧トリガーシステムのものに比べてトリガーシステムではオンボードメモリ容量が増加しており、FEE上に保持可能な PMT 波形データの量が増加している。これにより、近傍超新星爆発による超新

星ニュートリノイベントの検出可能量についても増加が期待されている。

|          | 旧トリガーシステム [13]              | トリガーシステム        |

|----------|-----------------------------|-----------------|

| FEE      | MoGURA                      | MoGURA2         |

| オンボードメモリ | 64 MB SD-RAM (うち 48 MB を使用) | 2 GB DDR4 メモリ×2 |

表 5.1: 旧トリガーシステムとトリガーシステムのオンボードメモリ容量

またデータ転送速度の向上を合わせて行うことで、オンボードメモリ上に蓄積するデータ量を 削減し中性子検出効率の向上を実現する。

#### 将来的なソフトウェアトリガー実装を可能とする柔軟性を持つこと

旧トリガーシステムではハードウェアを用いたイベント検出及びトリガーコマンドの発行が行われていた。このイベント検出では PMT ヒット本数の閾値判定による手法が主に用いられていた。

今後のさらなる背景事象減少を見据え、ハードウェアではなくソフトウェアを用いたイベント 検出及びトリガーコマンドの発行機能 (ソフトウェアトリガー) についての研究が進められてい る。ソフトウェアを用いることにより、従来のハードウェアに比べてより複雑な処理を用いたイ ベント検出が可能となる。そのほか高頻度なイベント検出手法の変更が可能であることや、ソフ トウェアはハードウェアトリガーのような基板への実装が可能なイベント検出処理量に対する物 理的な上限を持たないといった利点がある。

ソフトウェアトリガーでは、PMT のヒット本数情報の他に、PMT の波形情報やその位置の相関などを用いたイベント検出が検討されている。このような情報を利用することによって、従来の PMT のヒット本数閾値によるイベント選定ではこの閾値を超えなかったため物理イベントとして検出されなかった信号についても発光位置情報及び時間情報によってイベント検出が可能となり、インナーバルーン中の  $^{214}$ Po や  $^{14}$ C の低エネルギーイベントの検出が可能となると期待されている [14]。

#### Hitsum 算出の取り扱いを改善すること

Hitsum は PMT のヒット本数を表す信号の名称である。旧トリガーシステムにおいてイベント 検出にはこの Hitsum を利用しており、ケーブルを用いて全ての MoGURA ボードを一本の鎖状 に接続することで全 MoGURA ボードの Hitsum の加算を行なっていた。ボード故障時にはこの Hitsum の加算動作が途中で途切れることから、復旧時にはボード交換および複雑な再接続が必要 となりメンテナンス性の悪さが課題となった。

トリガーシステムにおいてもこの Hitsum を用いたイベント検出を行うことが検討されているため、旧トリガーシステムの課題点を踏まえた接続系の見直しを行うことでメンテナンス時における利便性の向上を目指す。

#### PTPv2 による時間情報取得に対応していること

KamLANDでは具体的な日時を表す時間情報 (以下絶対時間情報)の取得に GPS 受信機を用いており、ここからの時間情報伝達には IRIB-B と呼ばれる規格が用いられていた。IRIG-B では 1 秒間に一度絶対時間情報の送信を行っており、情報の伝達にはシリアル信号の変調方式を用いている。これにより、PMT の波形データを絶対時間と対応付けることが可能となるが、IRIG-B の関連製品の入手が難しくなっている現状がある。そこで、KamLAND2では IRIG-B の他に PTPv2 と呼ばれる規格についても導入予定となっている。PTPv2 では時間情報を伝えたいエレクトロニクス間で信号を一往復させることによって、信号遅延の測定および時間情報校正を行う手法をとっている。

#### 5.2 KamLAND2 のトリガーシステムデザイン

ここでは、KamLAND2のトリガーシステム導入の全体像及び具体的なトリガーシステムの説明をする。

始めに、KamLAND2のトリガー導入計画の全体を説明する。その後、本研究で着目するトリガー導入段階と具体的トリガーシステムデザインを示し、その機能を説明する。

#### 5.2.1 KamLAND2 へのトリガー導入計画

5.1 章でも触れた通り、KamLAND2 はソフトウェアトリガーの将来的な導入が計画されている。しかし、ソフトウェアトリガーのデータレートは膨大となる事が予想されており、このデータレートに対応したトリガー PC の入手およびシステムの構築には時間がかかることが予想される。そこで、ソフトウェアトリガー導入までの期間について、以下の 3 種類のトリガーシステムを段階的に運用することが検討されている。

#### ハードウェアトリガー系

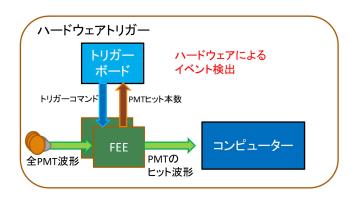

KamLAND2 建設後、最初に導入する予定となっているのが、ハードウェアトリガー系である。 ハードウェアトリガー系の概念図を図 5.1 に示す。PMT 信号を FEE で観測し、PMT ヒット本 数を出力する。この本数情報を用いてトリガーボードと呼ばれるハードウェアによってイベント 検出を行い、トリガーコマンドが発行される。このトリガーコマンドによってフロントエンドか ら波形情報がコンピュータへ送信される。

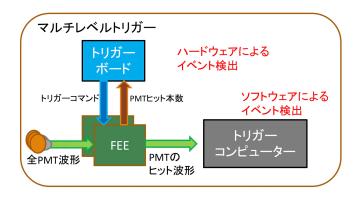

#### マルチレベルトリガー系

ハードウェアトリガー系による運用の後に導入される予定となっているのが、マルチレベルトリガー系である。マルチレベルトリガー系は、ハードウェアトリガー系と後述のソフトウェアトリガー系の中間状態のようなシステムとなっており、トリガー PC の導入が段階的に進められるため必要となる。

図 5.1: ハードウェアトリガーの概念図

図 5.2: マルチレベルトリガーの概念図

イベント検出の概念図を図 5.2 に示す。PMT 信号を FEE で観測し、PMT ヒット本数を出力する。これを用いてハードウェア系と同様にトリガーボードによるイベント検出を行う。その後、トリガーコンピューターへヒット波形が送られソフトウェアによるイベント検出が行われる。マルチレベルトリガー系は、ハードウェアによる粗い信号識別 (レベル 0) とソフトウェアトリガーによるイベント検出 (レベル 1) という形で、二段階の選定を行うことからこのように呼ばれる。

ここで、レベル 0 トリガーは PMT のダークヒット信号の排除によるデータ量の削減を目的としており、そのトリガー発行のヒット数閾値はハードウェアトリガーのそれと比べて大きく緩和したものとなっている。

その後のレベル1トリガーでは、ソフトウェアトリガーによる選定を行う。

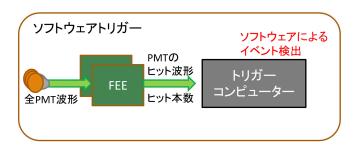

#### ソフトウェアトリガー系

トリガー PC が完全に導入された際の将来計画となっているのが、ソフトウェアトリガー系である。

ソフトウェアトリガーの概念図を図 5.3 に示す。この系では、FEE によって観測された全ヒット波形を送信し、トリガーコンピューターにてソフトウェアを用いたイベント選定のみを行う。

図 5.3: ソフトウェアトリガーの概念図

#### 5.3 KamLAND2 稼動初期を想定したトリガーシステムの構成

本項目では、トリガーシステムの全体像を具体的に示す。

始めにこのトリガーシステムが想定するトリガー導入段階を説明したのち、その全体像及び動作概要を示す。その後、主に使用するトリガーフラグの説明をする。

#### 5.3.1 想定するトリガー導入段階

5.2.1 章で述べた通り、KamLAND2 のトリガーシステムはトリガー PC の導入段階に応じた三種類があった。ここでは KamLAND 稼働初期に導入されるハードウェアトリガー系及びマルチレベルトリガー系への対応を可能とするトリガーシステムを示す。

#### 5.3.2 トリガーシステム全体図

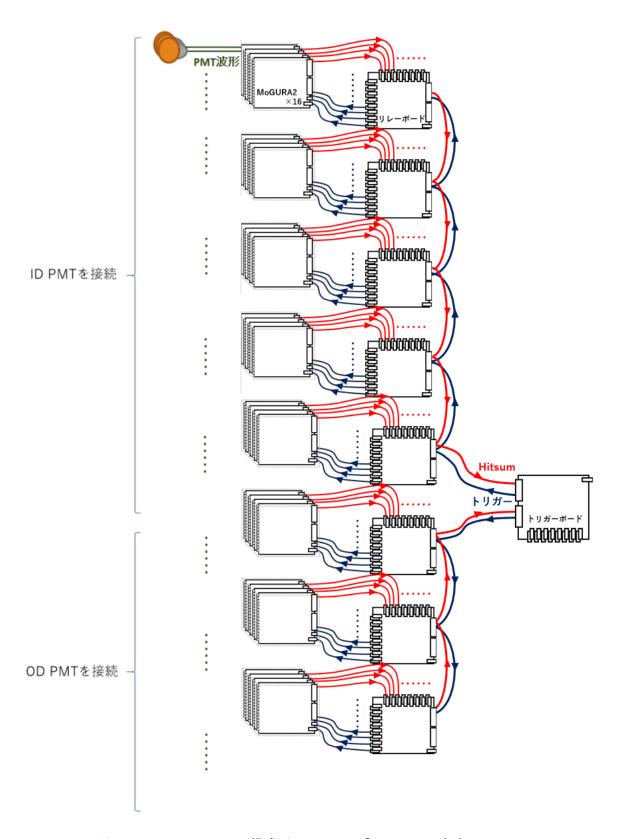

トリガーシステムの全体像を図5.4に示す。

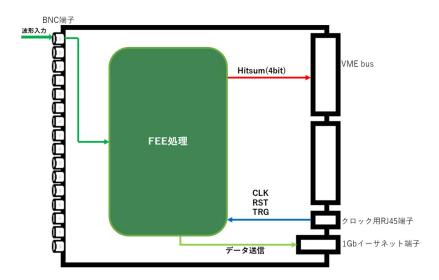

トリガーシステムは MoGURA2 とトリガーボード、それらを中継する役割を持つリレーボードと呼ばれるハードウェアによって構成される。MoGURA2 はトリガーシステムのために新たに開発された FEE であり、この MoGURA2 によって構成された部位をフロントエンドと呼ぶ。トリガーボードおよびリレーボードをバックエンドと呼ぶ。

PMT の信号線は MoGURA2 に接続され、ここで信号のデジタイズが行われる。MoGURA2 によってヒット判定を行ったのち、PMT のヒット本数である Hitsum がリレーボードを介してトリガーボードへ伝達される。その後、トリガーボードによってイベント検出が行われたのち、発行されるトリガーコマンドを MoGURA2 が受けることでデータ送信が行われる。

#### 5.3.3 想定される PMT 信号の特性

ここでは、トリガーシステムによって観測を目指す PMT 信号の特性を設定する。信号を特徴づける観点として、信号の大きさとイベントレートに着目する。

ここでは信号の特性の設定にとどめ、トリガーシステムの MoGURA2 がこれらの信号の検出

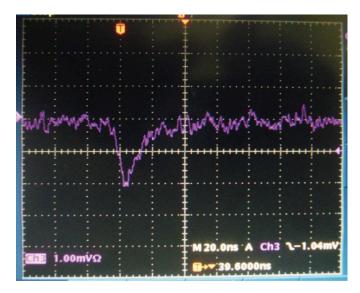

図 5.4: トリガーシステム模式図。クロック系については省略している。

図 5.5: 典型的な 1p.e. 波形 [9]。縦軸は 1 mV であり横軸は 20 ns となっている。

を可能とする性能にあるかについては後の6.2章で議論する。

#### 典型的な PMT 信号とその大きさ

MoGURA2 がデジタイズを行う PMT の信号は液体シンチレーターの発光によって生じた光電子を増幅して出力されており、その実態は負電圧のパルスである。この信号の最小単位は発光によって光子が 1 つ PMT に入射することによって生じる信号であり、これを 1p.e. と呼ぶ。典型的な 1p.e. 波形を図 5.5 に示す。このように 1p.e. イベントでは高さ-2 mV のパルスが観測され、時間にして 40 ns ほどの長さで検出される。

通常の物理イベントによる発光検出では数 p.e. の波形が検出されるが、宇宙線ミューオンによるイベント時には図 4.4 のような大光量イベントが検出され、そのピーク電圧はは-8 V にも上る。このイベント後にはアフターパルスが生じ、これを含めたイベント長は 50  $\mu$ s ほどとなる。

#### 物理イベントレート

PMT からの信号は物理イベントに起因する発光検出によるものと、熱電子の発生による物理イベントとは無関係の信号 (ダークヒット) に分けられる。これらの信号を合わせたイベントレートは 20 kHz となり、データストレージ容量の制限から全てを取得することは難しい。

そこでハードウェアを用いたトリガーによるイベント選定を行うことで、このダークヒットのデータを除いたデータ収集を行う。KamLAND の MoGDAQ では 100 Hz 程度のトリガーレートとなり $^{*1}$ 、これが物理イベントレートであると言える。この物理イベントレートには前述の宇宙線ミューオンのイベントが 0.3 Hz 含まれる。

<sup>\*1 2013</sup> 年 5 月 17 日を参照

#### PMT o Transit Time Spread

PMT による発光検出プロセスでは、光電子の走行時間の揺らぎによる検出までの時間広がりをもち、これを Transit Time Spread (T.T.S) と呼ぶ。KamLAND2 で導入予定の 20 inch 高量子効率 PMT (R12860-03LXA) は 2.4ns の T.T.S をもつ [15]。

#### 5.3.4 トリガーシステムの具体的な性能目標

ここでは、トリガーシステムの性能における具体的な数値目標をジッター及びレイテンシ差に対して設定する。ジッターとは同時信号入力時の MoGURA2 による検出時刻のばらつきを表し、レイテンシ差とは同時信号入力時の MoGURA2 による検出時刻に恒常的に存在するずれの大きさを表す。

この数値目標は同時信号を仮定して設定しているが、実際の KamLAND2 では PMT のケーブル長が異なるものを使用することが計画されており、そのケーブル遅延の差については考慮していない。そこで、PMT のケーブル長及びその補正方法についても説明する。

#### ジッターに対する目標

KamLAND2 で利用予定の PMT には T.T.S による数 ns オーダーの発光検出時間の広がりがあるが、物理イベント検出時には複数の PMT によってその発光を捉えることから、解析によってその影響を減少することが期待される。よって、ジッターを PMT の T.T.S より十分小さくしておくことはイベント再構成時の位置分解能向上につながるため重要である。本研究では、ジッターの性能目標を 0.1 ns とした。これは発光位置分解能で 2 cm に対応し、将来的な解析手法の最適化によるイベント再構成精度向上にも対応可能大きさである。

#### レイテンシ差に対する目標

KamLAND2 においては、レイテンシ差のような恒常的な信号検出時刻のずれに対してはレーザーキャリブレーションによる校正が行われる。この解析はオフラインによって行われており、その情報はデータ取得後の解析にのみ用いられる。本研究で想定するハードウェアを用いたトリガーシステムではトリガーボードによるイベント検出が行われるが、レイテンシ差は PMT のヒット本数情報出力に対する恒常的なずれを招き閾値判定に大きな影響を与える。そこで、本研究においてはこのレイテンシ差に対して 1 ns 以下という目標値を設定した。これは後述するMoGURA2 の H-gain による波形デジタイズのサンプリング間隔から与えた値である。

#### PMT ケーブル長の補正

KamLAND2 建設時には PMT のケーブル取り回し改善のため、複数種類のケーブル長の PMT を用いる。ケーブル長の差は最大で  $60\,\mathrm{m}$  になることが予想されており、信号のケーブル遅延は最大で  $300\mathrm{ns}$  ほどとなる。

このケーブル遅延に対し、MoGURA2 にリングバッファを実装することによる補正が考えられ

ている。リングバッファは MoGURA2 のオンボードメモリを利用し、ボード内の取得データを保持し一律で遅延する。こうして PMT の信号は MoGURA2 のボード単位での補正されるため、1 枚の MoGURA2 ボードに接続する PMT は同じケーブル長のものに限られる制限がある。

現在、KamLAND2 の PMT を近接するもの毎にグループ分けし、グループ毎の Hitsum を用いた中性子検出トリガーの研究が行われている。ここでは、ボードへの接続を PMT ケーブル長ではなくグループごとに行わなければならず、グループ内でケーブル長が異なる PMT が含まれる可能性がある。

こうした状況に対応するため、1 枚の MoGURA2 ボード内においても PMT の接続チャンネル毎にケーブル遅延の補正を行う機能の実装が期待される。ここでは、接続 PMT はその設置位置が近いことからそのケーブル長の差についても数 m 程度であることが想定される。

#### 5.3.5 トリガーシステム動作概要

ここでは、トリガーシステムの動作概要について説明する。トリガーシステムの動作はエレクトロニクスの同期駆動、時間情報の同期、イベント検出の3つの要素にわけられる。

#### エレクトロニクスの同期駆動

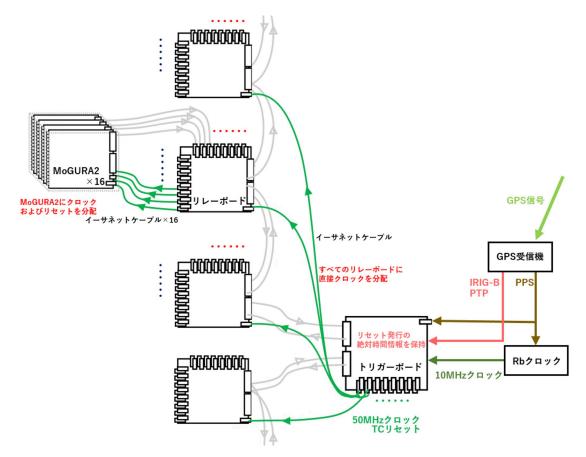

トリガーシステムの各エレクトロニクスはクロック信号と呼ばれる規定周波数の矩形信号を供給することによって駆動する。トリガーシステムでは全てのクロック信号は共通の基準クロックから生成されており、すべて同期している。ここではこのクロック信号の分配経路について説明する。

クロック信号分配を図 5.6 に示す。GPS 受信機から出力された PPS 信号を Rb クロックが受け、10 MHz クロック信号を生成する。トリガーボードは 10 MHz クロック信号から 50 MHz クロック信号を生成し、すべてのリレーボードへこれを分配する。その後、リレーボードによって各  $MoGURA2 \sim 50 \text{ MHz}$  クロック信号が分配される。

#### 時間情報の同期

前述のようにクロック信号分配を行うことで同期系によるエレクトロニクスの駆動を行うことができる。トリガーシステムによる波形取得ではフロントエンドによって波形情報及び時間情報を記録することが必要であり、同期駆動とは別にこの時間情報の同期を行う必要がある。

トリガーシステムのエレクトロニクスが持つ時間情報について説明する。時間情報はトリガーボード及び MoGURA2 が持つ。トリガーボードが持つのは GPS 受信機から IRIG-B もしくは PTPv2 方式によって送信された情報であり、これは具体的な日時を表す絶対時間情報である。それに対し、MoGURA2 はボードごとに独立した時間測定用のタイムカウンター (以下 TC) を持ち、これは 125 MHz のクロック信号の立ち上がり回数をカウントすることによって相対的な時間情報を持つ。TC の値はリセット時刻を基準とした経過時間の情報となっており、MoGURA2 より送信された波形データにはこの TC 値のみが記録されている。

トリガーシステムの時間情報同期にはトリガーシステムが持つ絶対時間情報と MoGURA2 が

図 5.6: トリガーシステムにおけるクロック及び TC リセットの分配経路

持つ相対的な時間情報を対応づけることが必要であり、その際に MoGURA2 の TC の値は全てのボードで一致させる必要がある。そこで、時間情報同期のためにトリガーボードから全てのMoGURA2 に同時に TC リセットを行い、この時の絶対時間情報をトリガーボードが記録する(図 5.6 を参照)。この時間情報同期を行うことで、MoGURA2 によって送信された波形データに記録された TC 値とリセットの絶対時間情報を合わせて取得波形の絶対時間情報を得ることができる。

#### イベント検出

イベント検出はトリガーボードによって Hitsum を観測し、その値の大きさや増加量などの要因を踏まえてトリガーコマンドをフロントエンドに対し発行することによって行われる。このトリガーコマンドによって MoGURA2 は波形取得及び TC 値の記録、送信を行う。

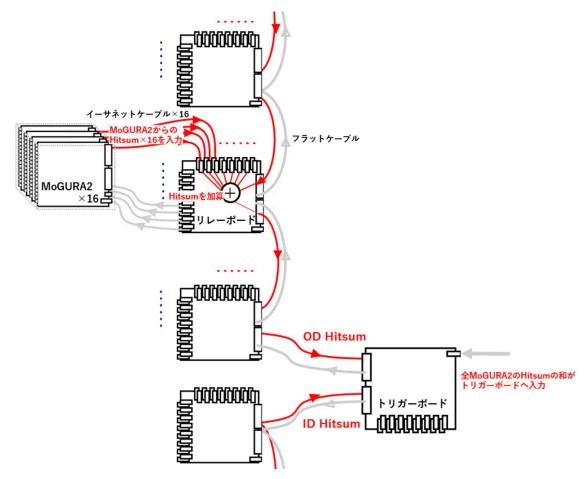

Hitsum の分配図を図 5.7 に示す。トリガーシステムの Hitsum 接続はトリガーボードから 2 系 統に分かれており、それぞれ ID と OD の Hitsum を独立して算出することが可能となっている。 MoGURA2 は 8 つの VME クレートに分配して接続され、このクレート単位でリレーボードに接続される。Hitsum はリレーボード単位で足し合わせたのち、リレーボードを ID、OD の系列 ごとにデイジーチェーン接続することによって各系列について Hitsum の加算がなされる。この

図 5.7: トリガーシステムにおける Hitsum の分配経路

ようにあらかじめリレーボードで Hitsum を加算しておくことで、MoGURA2 の故障時にも該当ボードからリレーボードに入力する Hitsum がなくなるだけで系全体における Hitsum 加算が途切れることはない。

トリガーコマンドの分配図を 5.8 に示す。トリガーコマンドは MoGURA2 に対して波形取得を命令するための信号である。トリガーボードから発行され、リレーボードを通じてフロントエンドへ入力される。

#### 5.3.6 主なトリガーフラグとトリガーコマンド

トリガーフラグとは、トリガーボードによってトリガーコマンドをフロントエンドへ送る際に トリガーボードによって記録される情報であり、発行されたトリガーコマンドの種別を表す。

トリガーシステムによるイベント検出に必要となるトリガーフラグの一例を以下に示す。ここでは MoGDAQ のトリガーフラグを参考にすることとし、トリガーシステムに導入することによる改善点に着目する。

• Single トリガー

図 5.8: トリガーシステムにおけるトリガーコマンドの分配経路

通常のイベント観測に用いる基本的なトリガー。検出器の大きさを考慮し、120 ns の時間窓によって累積した Hitsum (以下 Nhit) が閾値を超えた場合に発行され、フロントエンドではヒット波形のみ取得を行う。フロントエンドのオンボードバッファ容量増加に伴い、Nhit 閾値を下げより多くのデータを収集することが可能となると考えられる。

#### • Launch トリガー

宇宙線ミューオンの検出を目的としたトリガー。旧トリガーシステムと同様に Nhit 閾値が Single のものに比べて高く設定される。トリガーシステムでは OD Hitsum 情報を発行に 利用することができると考えられる。

#### • Adaptive トリガー

宇宙線ミューオン核破砕によって生じた不安定核の検出に用いる。フロントエンドのオンボードバッファ容量増加により、不安定核によって生じた中性子の検出効率が改善することが見込まれる。

#### • 1PPS トリガー

PPS 信号に同期して 1 秒間に一度発行され、ヒットに関わらず規定時間の全チャンネル波形取得を行う。

Baseline トリガー ヒットに関わらず全チャンネル波形取得を行う。 これらのトリガーフラグはヒット波形のみを取得するものとヒットに関わらず全チャンネルの波形を取得するものに分けることができ、フロントエンドの処理はそれぞれ異なる。そこでMoGURA2ではトリガーコマンドの入力を二種類に分け、ヒット波形のみを取得する Acquire hit トリガーとヒットに関わらず全チャンネルの波形を取得する Acquire range トリガーとして実装している。

#### 5.3.7 運用初期を想定したトリガーシステムのその他構想案

本章では、KamLAND2 運用初期を想定したトリガーシステムの説明を行ったが、ここで紹介した系の他にも、いくつかの系を構築することが可能である。

例えば、リレーボードのデイジーチェーン接続を廃止した系である。これによりリレーボード故障時にもヒット本数を取得できるほか、MoGURA2 に接続する PMT を KamLAND2 における PMT そのものの取り付け位置と対応させることで、MoGURA2 ボードの KamLAND2 における PMT 位置を対応付けたトリガー発行プロセスの開発も見込まれる。

# 第6章

# トリガーシステムにおけるエレクトロ ニクスの開発現状と本研究の目的

この章では、トリガーシステムにおけるエレクトロニクスと開発現状を踏まえて本研究の目標 を設定する。

始めに、トリガーシステムにおいて導入するエレクトロニクスの開発現状を説明する。その後、 現在開発されているトリガーシステムについて説明したのち、その現状を踏まえて本研究の目標 を設定する。

# 6.1 トリガーシステムに向けて新たに開発されるエレクトロニ クス

トリガーシステムについては 5 章で説明したが、このうち開発が必要となっているのは MoGURA2 とリレーボード、トリガーボードである。これらは全て FPGA を搭載した信号処理 機能を搭載しており、開発の段階は基板の設計および製造と FPGA ファームウェア開発の 2 段階 に分けられる。ここでは、使用予定の各エレクトロニクスの開発段階を紹介する。

フロントエンドを構成する MoGURA2 はその基盤設計及び製造が 3 枚完了している。このボードは研究開発を目的としており、KamLAND2 建設時には 140 枚生産する計画となっている。FPGA ファームウェアについても開発が進められており、MoGURA2 の単体系における波形の収集が可能となっている。この単体系の詳細については 6.4 章にて説明する。

リレーボード及びリレーボードについてはそのどちらも基板設計及び製造段階であり、ボード デザインのみが決定している。そのため、これらのエレクトロニクスを用いたトリガーシステム の開発は行われておらず、搭載する FPGA ファームウェアについても開発が行われていない。

# 6.2 新型フロントエンド電子回路 MoGURA2

MoGURA2 はトリガーシステムのために新たに開発された新型フロントエンド電子回路である。ボード外見は図 6.1 の様であり、PMT 波形の収集及び送信を行う役割を持つ。MoGURA2

図 6.1: MoGURA2 に搭載されている主な部品。LADC は画像面の背面に搭載されている。

は大容量なオンボードメモリを持ち、全中性子検出を目指した性能となっている。そのほか、波 形送信では 10 Gbps の光ファイバーによる高速データ通信が可能となっており、将来的なソフト ウェアトリガー導入を見据えた設計となっている。

ここでは、MoGURA2の性能及び各部の機能について説明する。

#### 6.2.1 MoGURA2 の性能と先行研究

これまでの先行研究により、MoGURA2 は単体系による波形取得が可能となっている。また、データ収集性能についても開発や検証が行われており、KamLAND2 のフロントエンドに求められる要求を満たす性能を持つことが確認されている。ここではデータ収集性能の観点として、デジタイズ及びデータレートの二つに着目し、MoGURA2 が要求性能を達成していることを説明する。

始めに、MoGURA2 のデジタイズ性能について説明した後、データレートの観点から説明する。

#### デジタイズ性能

トリガーシステムにおいては PMT 信号として高さ-2 mV の 1p.e. 信号から最大-8 V もの大き さとなるミューオン信号の検出を想定している。これらの信号検出を目指し、MoGURA2 のデジタイズにおいては以下のような性能が求められる。

| ゲインチャンネル     | H-gain         | L-gain    |  |

|--------------|----------------|-----------|--|

| 測定対象         | 1~50 p.e.      | ミューオン信号   |  |

| 使用 ADC       | RF-ADC         | ADS42LB69 |  |

| 測定レンジ        | +50 mV~-150 mV | +0 V∼-8 V |  |

| サンプリングレート    | 1 Gsps         | 250 Msps  |  |

| 分解能 (bit 換算) | 12 bit         | 16 bit    |  |

| ノイズ RMS      | $40~\mu V$     | 4.5 mV    |  |

表 6.1: MoGURA2 の各ゲインによるデジタイズ性能 [16]

- ノイズ RMS が十分小さく 2 mV の 1p.e. が検出可能であること

- 最大で-8 V の信号についてデジタイズが可能であること

ただしノイズ RMS については、KamLAND で運用されていたフロントエンドにおいて最も良い 値を記録した KamFEE の  $0.96~\mu V$  を基準とする。

この 8 V にもわたる広いレンジの信号を検出するため、MoGURA2 は H-gain と L-gain という二つのゲインチャンネルを実装している。すべての PMT 信号がこれら二つのゲインチャンネルによってそれぞれデジタイズされており、H-gain は  $1{\sim}50$  p.e. 程度の信号、L-gain はミューオンのような-数 V 程度の大光量信号を観測対象としている。

これらのデジタイズ性能の向上を目的とし、先行研究 [16] にて後述のアナログ子基板の最適化が行われた。この研究によって得られた H-gain および L-gain のデジタイズ性能を表 6.1 に示す。

H-gain は後述の RFSoC 搭載の RF-ADC によってデジタイズを行い、デッドタイムフリーな 1 Gsps でのデジタイズが可能となっている。分解能は 12 bit であり、これは  $+50 \, \text{mV}$  から- $150 \, \text{mV}$  を  $12 \, \text{bit}$  の二進数によってあらわすことを意味する。よって、この分解能をボード入力電圧に 換算すると

$$200[\text{mV}]/4095 = 48.8[\mu\text{V}] \tag{6.1}$$

と求められる。これは PMT の 1p.e. 波形の大きさである 2mV に比べて十分小さく、KamLAND で用いられていた MoGURA の P-gain の分解能 0.1mV より良いことがわかる。また、ノイズレベルについても KamFEE のノイズレベル  $0.96~\mu$ V から大きく改善されており、1p.e. 信号の検出に十分な性能を持つと言える。

L-gain のデジタイズには RFSoC 搭載のものではなく別部品としてボードに実装された ADC を用いており、デッドタイムフリーな  $250~{\rm Msps}$  でのデジタイズが可能となっている。ダイナミックレンジは  $0~{\rm V}$  から- $8~{\rm V}$  となっており、ミューオン信号の検出が可能なものとなっている。分解能は  $16~{\rm bit}$  であり、これを H-gain と同様にしてボード入力電圧に換算すると、

$$8[V]/65535 = 0.13[mV] \tag{6.2}$$

と求められる。これは MoGURA のミューオンイベント検出を想定したチャンネルである L-gain

の分解能 50 mV に比べて大きく改善されているといえる。ノイズ RMS は 4.5 mV となっており、これは KamLAND のミューオン信号用に利用されていた MoGURA の L-gain のノイズレベル 15.5 mV と比較すると大きく改善していることが分かる。

以上の議論より、MoGURA2のデジタイズのノイズ RMS が十分小さく 1p.e. 信号の検出が可能であり、ミューオン信号の検出が可能なダイナミックレンジを持つことが分かる。

#### データレート

トリガーシステムでは、イベントレートとして 100 Hz の通常イベント及び 0.3 Hz のミューオンイベントを想定した。これらのイベントの長さについては、通常イベントのを 1p.e. 波形と同じ 40 ns、ミューオンイベントについてはアフターパルスを含む  $50 \mu \text{s}$  と仮定した。

このイベントを踏まえて MoGURA2 で恒常的な波形取得に必要となるデータレートを計算する。MoGURA2 は 125 MHz のクロックによって駆動し、1 クロックの長さである 8 ns のデジタイズを 1 セットとしたデータフレームを構成する。デジタイズデータは 8 ns あたり 16 byte となっており、これにヘッダーとフッター合わせて 24 byte が付けられる。以上のことから、通常イベントを 16 ch すべてで検出した場合を仮定するとデータレートは

$$(16/8[byte/ns] \times 40[ns] + 24[byte]) \times 16[ch] \times 100[Hz] = 0.2[Mbyte/s]$$

(6.3)

と求められる。ミューオン信号についても同様に求めると、

$$(16/8[\text{byte/ns}] \times 50 \times 1000[\text{ns}] + 24[\text{byte}]) \times 16[\text{ch}] \times 0.3[\text{Hz}] = 0.5[\text{Mbyte/s}]$$

(6.4)

と求められる。これらを足し合わせることで、トリガーシステムにおいて恒常的なデータ収集を行う際に要求されるデータレートは  $0.7~{

m Mbyte/s}$  と求められる。

以上の要求を踏まえ、MoGURA2 によるデータ送信が可能なデータレートについて考察する。データレートを決定する要因は FPGA 及びオンボードメモリによるバッファリング速度とポートによるデータ転送速度に分けることができ、これらのレートを比較して速度が遅いものが MoGURA2 によって送信可能なデータレートとなる。

FPGA 及びオンボードメモリによるデータ処理能力については先行研究 [17] にて検証されており、恒常的に取得可能なヒットレートは最大で 480.77 kHz/Ch と算出されている。これをデータレートに直すと

$$480[kHz/Ch] \times 240[B] \times 16[Ch] = 1.7[GB/s]$$

(6.5)

と求められる。なお、この検証ではオンボードメモリの DDR4 メモリの代用として FPGA 搭載の UltraRAM を使用している。データ転送について MoGURA2 には SFP+ ポートを搭載しており、将来的に光通信による  $10~{\rm Gbps}$  が可能となる見込みである。これらのデータレートを比較することにより、将来的に MoGURA2 による恒常的な処理が可能なデータレートは最大で  $10~{\rm Gbps}$  (=1.25 GBps) となる。

以上の考察から、MoGURA2 は物理イベントを踏まえたデータレートに対応可能な性能を持つと言える。なお、将来的にはオンボードメモリとして実装されている DDR4 メモリを使用することでバッファ容量の拡大が可能となっている。

#### 6.2.2 MoGURA2 に実装されている主な入出力端子

MoGURA2 は以下に示す入出力端子を備えている。

#### BNC コネクタ

BNC コネクタは MoGURA2 のフロントパネルに 16 チャンネル搭載しており、PMT によって 出力された信号を入力するために用いる。ここから入力された信号はアナログ子基板による信号 増幅ののちにデジタイズされる。

#### LEMO コネクタ

LEMO コネクタは MoGURA2 のフロントパネルに二つ搭載されており、入力用のものと出力用がそれぞれひとつづつ実装されている。TTL 規格を満たす信号によるアクセスが可能となっており、検出器キャリブレーション時のトリガーへの利用が可能となっている。

#### 1GbE 用イーサネットコネクタ・SFP+ ポート

MoGURA2 にはイーサネット接続用のコネクタが 3 つ搭載されている。このうちの一つが 1 Gbps のイーサネットであり、残り二つが 10 Gbps 対応の SFP+ ポートとなっている。主な使用目的はスローコントロールおよび取得波形の転送である。

本研究ではスローコントロール及びデータ転送に 1 Gbps イーサネットを用いているが、将来的には 2 つの SFP+ ポートそれぞれをスローコントロールとデータ送信に用いる運用を想定している。

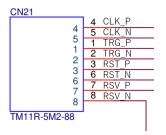

#### クロック用 RJ45 コネクタ

MoGuRA2 を駆動する際に必要となる 50~MHz クロックについて、RJ45 コネクタによる外部からの供給が可能となっている。

RJ45 コネクタのピンアサインを図 6.2 に示す。RJ45 コネクタは 4 bit の信号送受信が可能となっており、クロックを除く 3 bit 分の信号線を外部エレクトロニクスから MoGURA2 へのトリガーコマンドの入力や TC のリセットなどに用いる。

#### **VME**

MoGURA2 は VME クレートに設置した運用を想定しており、その駆動に必要となる電源は VME クレートから供給される。

VME の一部端子にデバッグ用コネクタが用意されており、バックプレーンの端子を介して 5 bit 分の信号の送受信が可能となっている。トリガーシステムではこの 5 bit のうち 4 bit を Hitsum を出力する目的で使用する予定となっている。

#### CLOCK\_INPUT(50MHz)

図 6.2: MoGURA2 へのクロック入力に用いる RJ45 コネクタのピン配置

#### その他デバッグ用コネクタ

以上に挙げたコネクタはすべてトリガーシステムでの利用が検討されているものであるが、これらのほかにボードのデバッグでのみ使用するコネクタが存在する。

JTAG は Xilinx 社製の Platform cable USB II の接続に使用し、外部のコンピュータから FPGA へのアクセスを可能とする。コンピュータ上で対応ソフトウェアを起動することで、FPGA ファームウェアに搭載したロジックアナライザによる内部信号の観測を行う。そのほか、FPGA 内部の信号に対し手動での制御を行うための VIO (Virtual i/o) の操作にも用いることができる。

そのほか、RFSoC の CPU をコマンドライン上で操作する際に有線接続によるパラレル通信が可能である。これは、外部のコンピュータで対応するターミナルソフトを起動することで CPU へのスローコントロールを行うことができる。スローコントロール自体はイーサネットを用いた SSH 接続によって可能であるが、IP アドレスの設定など SSH 接続のために必要となる操作にこれを用いる。

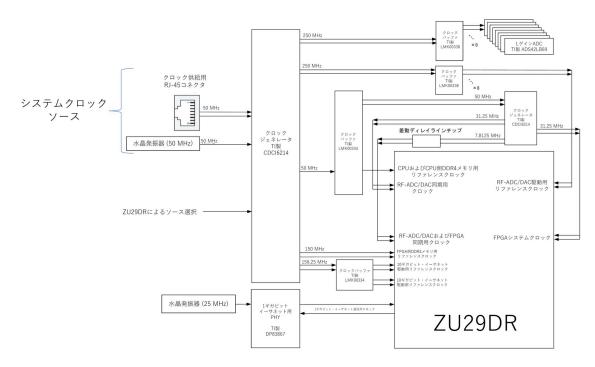

#### 6.2.3 クロック信号供給部

MoGURA2 の実装素子とクロック信号の分配図を図 6.3 に示す。前述のとおり MoGURA2 は 50 MHz のクロック信号を供給することで駆動する。しかし、ボード上のすべての素子が 50 MHz クロックで駆動しているわけではなく、クロックジェネレータ (CDCI6214) によって様々な周波数にこれを変換することで各部の素子を駆動している。

FPGA による信号処理は 125 MHz のシステムクロックによって行われており、このクロック生成には複数のクロックバッファが介在している。50 MHz のクロック信号が CDCI6214 によって 31.25 MHz に変換されたのち、ここから FPGA 内部のクロックジェネレータによって 125 MHz システムクロックが生成される。

CDCI6214 に対してはクロック用 RJ45 端子による外部から 50 MHz クロック信号の供給 (外部クロック) が可能である他、ボードに搭載された水晶発振器による供給 (内部クロック) も可能となっている。なお、外部クロックと内部クロックのそれぞれの特徴は以下のとおりである。

図 6.3: MoGURA2 のクロック系統図 [17]

#### • 外部クロック

MoGURA2 に搭載されたクロック供給用 RJ45 端子に 50MHz のクロックを供給すること で駆動する。複数の MoGURA2 に対し共通のクロックを入力することで同期した駆動が 可能となる。

#### • 内部クロック

MoGURA2 に搭載された水晶発振器によって生成された 50 MHz クロック信号によって 駆動する。外部からのクロック供給が不要である反面、水晶発振器の精度にバラツキが存 在することやクロック信号の位相を外部から調整する手段がないことから、同期系には使 用することができない。

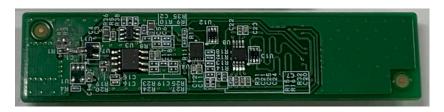

#### 6.2.4 アナログ子基板

MoGURA2 において信号処理を行うアナログ回路は図 6.4 のような子基板と呼ばれる別ボードへの実装を行うことによって MoGURA2 ボードから分離されており、回路の仕様変更や故障時の交換が容易になっている。アナログ子基板は MoGURA2 ボード 1 枚につき 16 枚取り付けられており、子基板 1 枚で 1 チャンネルの信号処理を行う。

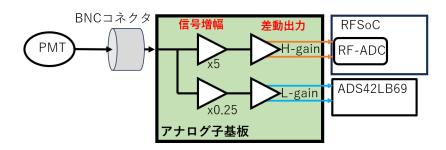

具体的な信号処理内容は、入力された PMT 信号の分岐及び信号の増幅である。その概念図を図 6.5 に示す。 入力信号を異なる増幅率によって増幅し H-gain 及び L-gain の 2 系統の ADC に入力することで、小さい分解能を持つ H-gain と大きなダイナミックレンジを持つ L-gain という二種類の波形デジタイズを実現している。なお、デジタイズ性能の詳細については表 6.1 で説明

図 6.4: アナログ子基板写真

図 6.5: アナログ子基板による信号の分岐及び増幅の概念図

しているため省略する。

このアナログ子基板については最適化が進められており、先行研究 [16] によってその低ノイズ 化や部品選定が行われた。

#### 6.2.5 LADC

MoGURA2 には、L-gain のデジタイズを目的とした ADC (型番 ADS42LB69) が実装されている。これを LADC と呼び、16bit の分解能による 250MHz でのサンプリングが可能である。

#### 6.2.6 RFSoC と FPGA ファームウェア

MoGURA2 の主な処理は、ボードに一つ搭載された RFSoC (型番 XCZU29DR-1FFVF1760E) によって行われる。RFSoC (RF System on Chip) は FPGA、DAC、ADC、CPU が複合した素子である。これにより、動作の高速化や省電力化、基板開発期間の短縮が可能となるなどの利点がある。

RFSoC に搭載されている FPGA ファームウェアの主な機能ブロックを以下に示す。

#### RFDC ブロック

RFDC ブロックの役割は H-gain 波形のデジタイズであり、RF-ADC によって行われる。RF-ADC は前述の RFSoC 搭載の ADC の名称であり、FPGA との高速なデータ通信が可能となっている。

| HEADER[7:0] (0xAA) | FW_VERSIO  | N[7:0]      | DF_VERSION[7:0]  | SERIAL[11:0] |             | CH_ID[11:0] | FRAME_LENGTH[11:0] | FRAME_INFO[3:0] |

|--------------------|------------|-------------|------------------|--------------|-------------|-------------|--------------------|-----------------|

| RESERVED[15:0]     |            |             | TIME_STAMP[47:0] |              |             |             |                    |                 |

| HADC0[11:0]        |            | HADC1[11:0] |                  | HADC2[11:0]  |             | HADC3[11:0] | LADC0[15:0]        |                 |

| HADC4[11:0]        |            | HADC5[11:0] |                  | HADC7[11:0]  |             | HADC7[11:0] | LADC1[15:0]        |                 |

| HADC0[11:0]        |            | HADC1[11:0] |                  | HADC2[11:0]  |             | HADC3[11:0] | LADC0[15:0]        |                 |

| HADC4[11:0]        |            | HADC5[11:0] |                  | HADC7[11:0]  |             | HADC7[11:0] | LADC1[15:0]        |                 |

| HADC0[11:0]        |            | HADC1[11:0] |                  | HADC2[11:0]  |             | HADC3[11:0] | LADC0[15:0]        |                 |

| HADC4[11:0]        |            | HADC5[11:0] |                  | HADC7[11:0]  |             | HADC7[11:0] | LADC1[15:0]        |                 |

| FOOTER[7:0] (0x55) | TRIGGER_ID | [23:0]      |                  |              | DF_ID[31:0] |             |                    |                 |

図 6.6: MoGURA2 のデータフレームフォーマット

#### トリガーブロック

トリガーブロックの主な役割は、H-gain 波形に対するヒット判定およびヒット波形のデータフレーム作成である。

ヒット判定では、RF-ADC によってデジタイズされた入力信号の電圧値が設定閾値を超えている間の観測波形についてヒットフラグを立てる処理を行う。閾値については各チャンネルで独立に設定をすることが可能となっており、このヒットフラグが生じた数を Hitsum として扱う。

データフレームの作成では、MoGURA2 ファームウェア内部において時間情報を持つタイムカウンター (TC) の情報と H-gain、L-gain 波形データ、取得チャンネルの情報などによって 1 つのデータのブロックを構成する。現在 MoGURA2 で利用されているデータフレームのフォーマットを図 6.6 に示す。

#### バッファーブロック

バッファーブロックはトリガーブロックによって作成されたデータフレームを一時的に保持しておく役割を持つ。データ転送を行う際にこのデータフレームを後述のトランスファーブロックに出力する。

#### トランスファーパート

トランスファーパートは、バッファーブロックのデータフレームを RFSoC 上の CPU に読み出す役割を持つ。CPU 上に読み出されたデータはイーサネットを介して、ZeroMQ と呼ばれるライブラリを用いたパケット通信によって送信される。

#### DDR4 メモリ

MoGURA2 には、RFSoC からのデータを保持するオンボードメモリとして DDR4 メモリが 6 つ搭載されている。これらは RFSoC のアクセス方法によって分けられ、Processing Logic (= FPGA の論理回路) によるアクセスが可能な PL DDR が 2 つと Processing System (= RFSoC 上の CPU) によるアクセスが可能な PS DDR が 4 つとなっている。役割はデータ送信前のデータ バッファリングであり、トリガーブロックによって作成されたデータフレームの保持を行う。

メモリ仕様は表 6.2 のようになっている。

|        | 型番                      | 容量 [Gbyte]<br>(ダイ当たり) | ダイ数 | 容量 [Gbyte]<br>(合計) | データレート [Gbyte/s]<br>(最大) |

|--------|-------------------------|-----------------------|-----|--------------------|--------------------------|

| PL DDR | MT40A1G16KD-062E IT:E   | 1                     | 4   | 4                  | 約 9.6                    |

| PS DDR | MT40A512M16LY-062E IT:E | 2                     | 2   | 4                  | 約 19.2                   |

表 6.2: MoGURA2 に搭載されているオンボードメモリ [17]

#### 6.3 バックエンドに用いるエレクトロニクス

バックエンド電子回路はリレーボード及びトリガーボード、GPS 受信機と Rb クロックによって構成される。ここでは、トリガーシステムに関係するリレーボード及びトリガーボードについてのみ説明する。

リレーボード及びトリガーボードは現在設計段階であるため、ここでは現在決定しているこれ らのボードデザインについて説明する。

#### 6.3.1 リレーボードのデザイン

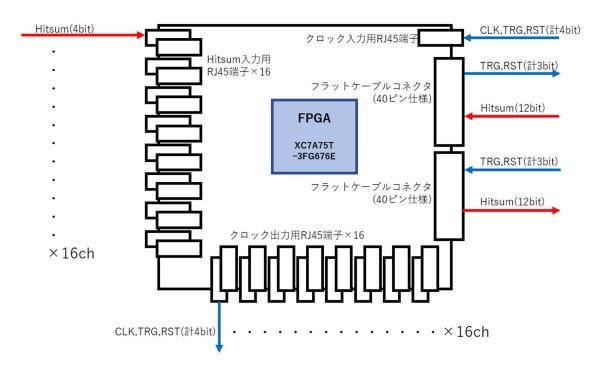

リレーボードのデザインは図 6.7 のようになっている。FPGA (XC7A75T-3FG676E) を搭載し、クロック入力用 RJ45 端子に 50 MHz のクロックを供給することで駆動する。フラットケーブルコネクタ 2 つを実装しており、一つは他のリレーボードから Hitsum を受けトリガーを出力するため、もう一つは反対に他のリレーボードからトリガーを受け Hitsum を出力するためのものとなっている。MoGURA2 に接続するための RJ45 コネクタを計 32 個実装しており、うち 16 個はクロックおよびトリガーを供給に使用し、残り 16 個は Hitsum を受けるために使用する。

#### 6.3.2 トリガーボードのデザイン

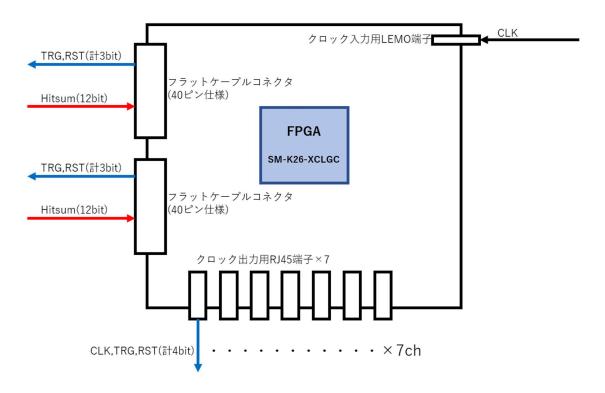

トリガーボードのデザインは図 6.8 のようになっている。FPGA (XC7A75T-3FG676E) を搭載し、Rb クロックによって生成された 10 MHz クロックを LEMO 端子から供給することで駆動する。このクロックを元に 50 MHz クロックを生成し、トリガー信号とともに RJ45 端子よりリレーボードへ供給する。また、40 ピン仕様のフラットケーブルコネクタを二つ備え、2 枚のリレーボードとトリガー信号および Hitsum の送受信が可能となっている。

# 6.4 MoGURA2 を用いたトリガーシステムの現状

ここでは、これまで開発されている MoGURA2 のトリガーシステムを説明する。

図 6.7: 現在想定されているリレーボードのデザイン。トリガーシステムに関連する入出力信号についても記載した。

図 6.8: 現在想定されているトリガーボードのデザイン。トリガーシステムに関連する入出力信号についても記載した。

図 6.9: 現在波形取得が可能となっている系

#### 6.4.1 MoGURA2 単体系での動作試験

前述のようにトリガーシステムにおけるバックエンドのエレクトロニクスは製造段階であり使用することができないため、これまで MoGURA2 を 1 枚用いた単体系による波形取得のみ行われてきた。

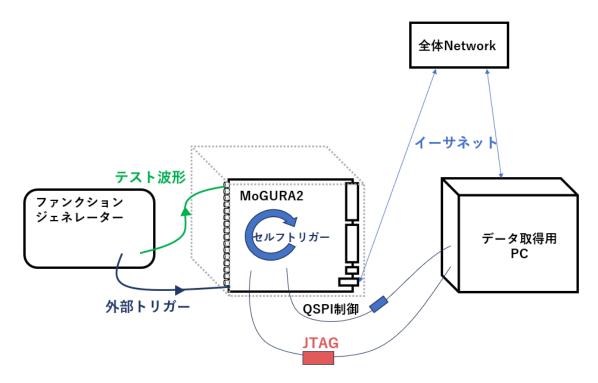

波形の取得が可能となっている系を図 6.9 に示す。MoGURA2 の制御には共通のネットワークに接続されたデータ取得用 PC を利用し、シリアル通信もしくはイーサネットによってMoGURA2 のスローコントロールを行う。また、取得データはイーサネットを用いたパケット通信によってデータ取得用 PC に送信される。そのほか、デバッグ用に Xilinx 社の Platform Cable USB II を用いた FPGA 内部信号の観測や一部制御を行っている。なお、将来的には全ての制御をイーサネットを用いた SSH 接続に移行する予定となっている。

外部エレクトロニクスによるトリガーコマンドには対応しておらず、波形取得にはテスト用の 以下の2つのトリガーが使用可能である。

- セルフトリガー 入力波形に対し MoGURA2 内部で閾値判定を行い、これを超える波形が検出された場合

- 人力波形に対し MoGURA2 内部で閾値判定を行い、これを超える波形が検出された場合に波形取得を行う。

- 外部強制トリガー 波形とともに外部からトリガー信号を入力し、その信号入力時間分の波形をヒット数と関

6.5 本研究の目的 59

係なく取得する。MoGURA2のフロントパネルに搭載された入力用 LEMO 端子を用いた TTL 規格の入力に対応している。

これらのトリガーは MoGURA2 単体系を想定し開発されたものであり、複数同期系によるトリガーシステムには使用することができない。

#### 6.5 本研究の目的

MoGURA2 同期系を想定したトリガーシステムが開発されていない現状を踏まえ、本研究ではトリガーインターフェースの開発を行い、MoGURA2 同期系によるデータ取得の検証を行うことを目的とした。そのために、MoGURA2 2 枚とバックエンド回路を模擬した Xilinx 評価ボード(ZCU102)1 枚を用いた系で同期性の検証を行う。

#### 6.5.1 同期系における目標性能

本研究においては、同時信号に対する波形検出時刻の一致精度に対して目標値を定め、同期の 検証を行う。トリガーシステムの性能目標を踏まえ、ジッターとして 0.1 ns、レイテンシの差と して 1 ns と定めた。

#### 6.5.2 本研究の流れ

本研究では、はじめに同期系による波形取得を行うためにファームウェアに搭載する FPGA ロジックの開発を行った。その後、それらのロジックの動作確認を MoGURA2 の単体系で行ったのち、2 枚の MoGURA2 と ZCU102 を用いた同期系による波形取得試験を行った。

開発したロジックの概要を 7 章、動作確認については 8 章、MoGURA2 複数同期系における波形取得試験及びその結果については 9 章で説明する。

### 第7章

# MoGURA2 同期系による同期波形取得 のための FPGA ロジック開発

この章では、本研究にて開発した FPGA ロジックについて説明する。

はじめに、トリガーシステムによる波形取得の際に必要となる要素をまとめる。その後、本研究にて開発した FPGA ロジックに含まれる機能モジュールの概要を説明する。

### 7.1 トリガーシステム実現のために必要な要素

ここでは、トリガーシステム実現のために必要となる要素についてまとめる。 トリガーシステムにおいて、以下の 5 つの機能が必要となる。

- PMT 信号に対するヒット判定機能

- Hitsum 出力機能

- 外部クロックによる同期駆動

- トリガーコマンドのインターフェース

- TC リセット機能による時間情報同期

これらのうち、ヒット判定及び Hitsum 出力機能、外部クロックによる同期駆動についてはすでに 開発されており、すでにファームウェアに実装されている。トリガーコマンドのインターフェース及び TC リセット機能については利用されておらず、ファームウェアへの実装が必要である。

#### 7.1.1 すでに開発されている機能

前述の通り、ヒット判定機能及び Hitsum 出力機能についてはすでに実装されている。ここでは、これらの機能の概要を紹介する。

#### ヒット判定機能

ヒット判定機能はデジタイズ波形があらかじめ設定したヒット閾値を超えた際にヒット信号と 判別する機能である。

MoGURA2 ではデッドタイムフリーなデジタイズがなされており、そのデジタイズデータは常に流れ続けている。この連続したデジタイズデータのうちヒット波形を区別するために、HIT\_FLAG と呼ばれる信号が用いられている。具体的な手法としては閾値による判定が採用されており、PMT 信号が設定された閾値を超えている間だけ HIT\_FLAG は 1 を出力するものとなっている。ヒット判定より後段の処理では、この HIT\_FLAG の値を参照することでヒット波形の処理が可能となっている。

このヒット機能判定は MoGURA2 に実装された 16Ch の全 BNC 端子に実装されており、閾値についても各チャンネルごとに独立に設定することができる。また、ヒット判定の前後拡張機能があり閾値を実際に超えたデータの前後 1 クロック分のデータについても HIT\_FLAG が 1 となるよう設計されている。

#### Hitsum 出力機能

PMT のヒット本数情報である Hitsum は前述の HIT\_FLAG を元に算出されている。具体的には、HIT\_FLAG が 0 から 1 に変化したチャンネル数をカウントしその数を 4 bit で出力している。本研究においては、Hitsum 出力に使用可能な信号線は 4 bit 分しか用意されておらず、Hitsum が 4 bit で表現できない 16 の場合については代わりに 15 を出力するよう変更を行なっている。そのほか、後述のトリガーシステムの起動に必要となるため Hitsum の出力を停止する機能についても新たに実装した。

#### 外部クロックによる同期駆動